# Pai Semi

# Enhanced ESD, 3.0 kV rms 200Mbps Single-Channel Digital Isolators

# **Data Sheet**

#### FEATURES

Ultra-low power consumption (1Mbps): 0.75mA/Channel High data rate: 200Mbps High common-mode transient immunity: 75 kV/µs typical High robustness to radiated and conducted noise Low propagation delay: 8 ns typical for 5 V operation 9 ns typical for 3.3 V operation Isolation voltages: AC 3000Vrms High ESD rating: ESDA/JEDEC JS-001-2017 Human body model (HBM) ±8kV Safety and regulatory approvals: UL certificate number: E494497 3000Vrms for 1 minute per UL 1577 **CSA Component Acceptance Notice 5A** VDE certificate number: 40053041 DIN VDE V 0884-11:2017-01 VIORM = 565V peak CQC certification per GB4943.1-2011 3 V to 5.5 V level translation Wide temperature range: -40°C to 125°C **RoHS-compliant, NB SOIC-8 package** APPLICATIONS **General-purpose Single-channel isolation** Industrial field bus **Isolation Industrial automation systems**

Isolated switch mode supplies Isolated ADC, DAC

Motor control

#### **GENERAL DESCRIPTION**

The  $\pi 1 xxxxx$  is a 2PaiSemi digital isolators product family that includes over hundreds of digital isolator products. By using maturated standard semiconductor CMOS technology and 2PaiSEMI *iDivider*<sup>®</sup> technology, these isolation components provide outstanding performance characteristics and reliability superior to alternatives such as optocoupler devices and other integrated isolators.

Intelligent voltage divider technology (*iDivider*<sup>®</sup> technology) is a new generation digital isolator technology invented by 2PaiSEMI. It uses the principle of capacitor voltage divider to transmit voltage signal directly cross the isolator capacitor without signal modulation and demodulation.

The  $\pi$ 1xxxxx isolator data channels are independent and are available in a variety of configurations with a withstand voltage rating of 1.5 kV rms to 6.0 kV rms and the data rate from DC up to

600Mbps (see the Ordering Guide). The devices operate with the supply voltage on either side ranging from 3.0 V to 5.5 V, providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. The fail-safe state is available in which the outputs transition to a preset state when the input power supply is not applied.

$\pi$ 110E3

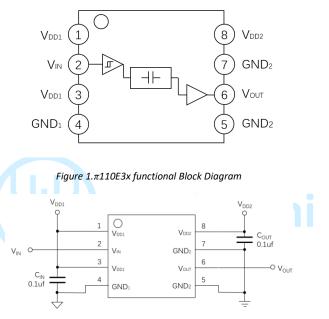

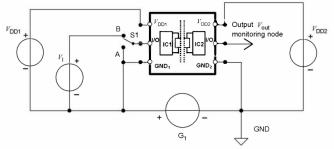

#### FUNCTIONAL BLOCK DIAGRAMS

Figure 2.π110E3x Typical Application Circuit

Room 307-309, No.22, Boxia Road, Pudong New District, Shanghai, 201203, China 021-50850681 2Pai Semiconductor Co., Limited. All rights reserved. http://www.rpsemi.com/

#### Rev.1.8

Information furnished by 2Pai semi is believed to be accurate and reliable. However, no responsibility is assumed by 2Pai semi for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of 2Pai semi. Trademarks and registered trademarks are the property of their respective owners.

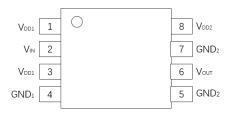

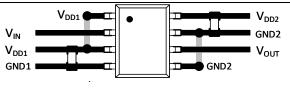

# PIN CONFIGURATIONS AND FUNCTIONS

Table 1. $\pi$ 110E3x Pin Function Descriptions

| Pin No. | Name             | Description                                                     |

|---------|------------------|-----------------------------------------------------------------|

| 1       | Vdd1             | Supply Voltage for Isolator Side 1.                             |

| 2       | Vin              | Logic Input.                                                    |

| 3       | V <sub>DD1</sub> | Supply Voltage for Isolator Side 1.                             |

| 4       | $GND_1$          | Ground 1. This pin is the ground reference for Isolator Side 1. |

| 5       | $GND_2$          | Ground 2. This pin is the ground reference for Isolator Side 2. |

| 6       | Vout             | Logic Output.                                                   |

| 7       | GND <sub>2</sub> | Ground 2. This pin is the ground reference for Isolator Side 2. |

| 8       | Vdd2             | Supply Voltage for Isolator Side 2.                             |

Figure 3. $\pi$ 110E3x Pin Configuration

## **ABSOLUTE MAXIMUM RATINGS**

T<sub>A</sub> = 25°C, unless otherwise noted.

Table 2.Absolute Maximum Ratings<sup>4</sup>

| Parameter                                                                                  | Rating                             |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------|--|--|

| Supply Voltages (V <sub>DD1</sub> -GND <sub>1</sub> , V <sub>DD2</sub> -GND <sub>2</sub> ) | –0.5 V to +7.0 V                   |  |  |

| Input Voltages <sup>1</sup>                                                                | –0.5 V to V <sub>DDx</sub> + 0.5 V |  |  |

| Output Voltages <sup>1</sup>                                                               | –0.5 V to V <sub>DDx</sub> + 0.5 V |  |  |

| Average Output Current per Pin <sup>2</sup> Side 1 Output Current ( $I_{O1}$ )             | –10 mA to +10 mA                   |  |  |

| Average Output Current per Pin <sup>2</sup> Side 2 Output Current (I <sub>02</sub> )       | -10 mA to +10 mA                   |  |  |

| Common-Mode Transients Immunity 3                                                          | -200 kV/μs to +200 kV/μs           |  |  |

| Storage Temperature (T <sub>ST</sub> ) Range                                               | –65°C to +150°C                    |  |  |

| Ambient Operating Temperature (T <sub>A</sub> ) Range                                      | –40°C to +125°C                    |  |  |

Notes:

$^{1}V_{\text{DDx}}$  is the side voltage power supply V\_D, where x = 1 or 2.

<sup>2</sup> See Figure 4 for the maximum rated current values for various temperatures.

<sup>3</sup> See Figure 11 for Common-mode transient immunity (CMTI) measurement.

<sup>4</sup> Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                       | Symbol                        | Min                               | Тур | Max                               | Unit |

|---------------------------------|-------------------------------|-----------------------------------|-----|-----------------------------------|------|

| Supply Voltage                  | V <sub>DDx</sub> <sup>1</sup> | 3                                 |     | 5.5                               | V    |

| High Level Input Signal Voltage | VIH                           | 0.7*V <sub>DDx</sub> <sup>1</sup> |     | V <sub>DDx</sub> <sup>1</sup>     | V    |

| Low Level Input Signal Voltage  | VIL                           | 0                                 |     | 0.3*V <sub>DDx</sub> <sup>1</sup> | V    |

| High Level Output Current       | Іон                           | -6                                |     |                                   | mA   |

| Low Level Output Current        | lol                           |                                   |     | 6                                 | mA   |

| Data Rate                       |                               | 0                                 |     | 200                               | Mbps |

| Junction Temperature            | Τı                            | -40                               |     | 150                               | °C   |

| Ambient Operating Temperature   | T <sub>A</sub>                | -40                               |     | 125                               | °C   |

Notes:

$^{1}$  V<sub>DDx</sub> is the side voltage power supply V<sub>DD</sub>, where x = 1 or 2.

Table 4. $\pi$ 110xxx Truth Table

| V <sub>ix</sub> Input <sup>1</sup> | V <sub>DDI</sub> State <sup>1</sup> | V <sub>DDO</sub> State <sup>1</sup> | Default Low<br>Vox Output <sup>1</sup> | Default High<br>Vox Output <sup>1</sup> | Test Conditions<br>/Comments |

|------------------------------------|-------------------------------------|-------------------------------------|----------------------------------------|-----------------------------------------|------------------------------|

| Low                                | Powered <sup>2</sup>                | Powered <sup>2</sup>                | Low                                    | Low                                     | Normal operation             |

| High                               | Powered <sup>2</sup>                | Powered <sup>2</sup>                | High                                   | High                                    | Normal operation             |

| Open                               | Powered <sup>2</sup>                | Powered <sup>2</sup>                | Low                                    | High                                    | Default output               |

| Don't Care <sup>4</sup>            | Unpowered <sup>3</sup>              | Powered <sup>2</sup>                | Low                                    | High                                    | Default output⁵              |

| Don't Care <sup>4</sup>            | Powered <sup>2</sup>                | Unpowered <sup>3</sup>              | High Impedance                         | High Impedance                          |                              |

Notes:

$^{1}V_{lx}/V_{0x}$  are the input/output signals of a given channel (A or B).  $V_{DDI}/V_{DD0}$  are the supply voltages on the input/output signal sides of this given channel.

$^2$  Powered means V\_DDx  $\geq 2.95$  V

$^3$  Unpowered means V\_{DDx} < 2.30V

$^{4}$  Input signal (V<sub>Ix</sub>) must be in a low state to avoid powering the given V<sub>DDI</sub><sup>1</sup> through its ESD protection circuitry.

<sup>5</sup> If the V<sub>DDI</sub> goes into unpowered status, the channel outputs the default logic signal after around 1us. If the V<sub>DDI</sub> goes into powered status, the channel outputs the input status logic signal after around 1us.

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

Table 5.Switching Specifications

$V_{DD1} - V_{GND1} = V_{DD2} - V_{GND2} = 3.3V_{DC} \pm 10\%$  or  $5V_{DC} \pm 10\%$ ,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                                 | Symbol                         | Min | Тур | Max  | Unit   | Test Conditions/Comments                                                               |  |

|-------------------------------------------|--------------------------------|-----|-----|------|--------|----------------------------------------------------------------------------------------|--|

| Minimum Pulse Width                       | PW                             |     |     | 5    | ns     | Within pulse width distortion (PWD) limit                                              |  |

| Maximum Data Rate                         |                                | 200 |     |      | Mbps   | Within PWD limit                                                                       |  |

| Dranagation Dalay Tima <sup>1</sup>       |                                | 5.5 | 8   | 12.5 | ns     | @ 5V <sub>DC</sub> supply                                                              |  |

| Propagation Delay Time <sup>1</sup>       | tphl, tplh                     | 6.5 | 9   | 13.5 | ns     | @ 3.3V <sub>DC</sub> supply                                                            |  |

|                                           |                                | 0   | 0.3 | 3.0  | nc     | The max different time between $t_{\mbox{\tiny PHL}}$ and $t_{\mbox{\tiny PLH}} @$     |  |

| Pulse Width Distortion                    | PWD                            | 0   | 0.5 | 5.0  | ns     | $5V_{\text{DC}}$ supply. And The value is $\mid t_{\text{pHL}}$ - $t_{\text{pLH}}\mid$ |  |

|                                           |                                | 0   | 0.3 | 3.0  | ns     | @ 3.3V <sub>DC</sub> supply                                                            |  |

|                                           |                                |     |     |      |        | The max different propagation delay time                                               |  |

| Part to Part Propagation Delay            | tрsк                           |     |     | 2    | ns     | between any two devices at the same                                                    |  |

| Skew                                      | LPSK                           |     |     |      |        | temperature, load and voltage @ 5V <sub>DC</sub> supply                                |  |

|                                           |                                |     |     | 2    | ns     | @ 3.3V <sub>DC</sub> supply                                                            |  |

| Output Signal Rise/Fall Time <sup>4</sup> | t <sub>r</sub> /t <sub>f</sub> |     | 1.5 |      | ns     | See Figure 7.                                                                          |  |

| Dynamic Input Supply Current per          |                                |     | 9   |      | μΑ     | Inputs switching, 50% duty cycle square wave,                                          |  |

| Channel                                   | DDI (D)                        |     | 9   |      | /Mbps  | CL = 0 pF @ 5V <sub>DC</sub> Supply                                                    |  |

| Dynamic Output Supply Current             | DDO (D)                        |     | 38  |      | μΑ     | Inputs switching, 50% duty cycle square wave,                                          |  |

| per Channel                               | IDDO (D)                       |     | 30  |      | /Mbps  | CL = 0 pF @ 5V <sub>DC</sub> Supply                                                    |  |

| Dynamic Input Supply Current per          | DDI (D)                        |     | 5   |      | μΑ     | Inputs switching, 50% duty cycle square wave,                                          |  |

| Channel                                   | (ט) וטטו                       |     | J   |      | /Mbps  | $CL = 0 pF @ 3.3V_{DC}Supply$                                                          |  |

| Dynamic Output Supply Current             | DDO (D)                        |     | 23  |      | μΑ     | Inputs switching, 50% duty cycle square wave,                                          |  |

| per Channel                               | IDDO (D)                       |     | 25  |      | /Mbps  | $CL = 0 pF @ 3.3V_{DC}Supply$                                                          |  |

| Common-Mode Transient                     | СМТІ                           |     | 75  |      | k)//uc | $V_{IN} = V_{DDx}^2 \text{ or } 0V, V_{CM} = 1000 \text{ V}$                           |  |

| Immunity <sup>3</sup>                     | CIVITI                         |     | 75  |      | kV/μs  | v <sub>IN</sub> - v <sub>DDx</sub> OI OV, v <sub>CM</sub> - 1000 v                     |  |

| Jitter                                    |                                |     | 120 |      | ps p-p | See the Jitter Measurement section                                                     |  |

| JILLEI                                    |                                |     | 20  |      | ps rms |                                                                                        |  |

| ESD(HBM - Human body model)               | ESD                            |     | ±8  |      | kV     |                                                                                        |  |

Notes:

$^{1}$ t<sub>pLH</sub> = low-to-high propagation delay time, t<sub>pHL</sub> = high-to-low propagation delay time. See Figure 8.

$^2\,V_{\text{DDx}}$  is the side voltage power supply V\_DD, where x = 1 or 2.

<sup>3</sup> See Figure 11 for Common-mode transient immunity (CMTI) measurement.

<sup>4</sup> tr means is the time from 10% amplitude to 90% amplitude of the rising edge of the signal, tf means is the time from 90% amplitude to 10% amplitude of the falling edge of the signal.

#### Table 6.DC Specifications

VDD1 - VGND1 = VDD2 - VGND2 = 3.3VDC±10% or 5VDC±10%, TA=25°C, unless otherwise noted.

|                                                              | Symbol           | Min                                | Тур                    | Max               | Unit | Test Conditions/Comments                 |

|--------------------------------------------------------------|------------------|------------------------------------|------------------------|-------------------|------|------------------------------------------|

| Rising Input Signal Voltage Threshold                        | V <sub>IT+</sub> |                                    | $0.6*V_{DDx}^{1}$      | $0.7*V_{DDx}^{1}$ | V    |                                          |

| Falling Input Signal Voltage Threshold                       | V <sub>IT-</sub> | 0.3* V <sub>DDX</sub> <sup>1</sup> | $0.4* V_{DDX}^1$       |                   | V    |                                          |

| High Lough Output Valtage                                    | Voh 1            | V <sub>DDx</sub> - 0.1             | V <sub>DDx</sub>       |                   | V    | –20 μA output current                    |

| High Level Output Voltage                                    | VOH -            | V <sub>DDx</sub> - 0.2             | V <sub>DDx</sub> - 0.1 |                   | V    | -2 mA output current                     |

| Low Loval Output Valtage                                     | Vol              |                                    | 0                      | 0.1               | V    | 20 μA output current                     |

| Low Level Output Voltage                                     | VOL              |                                    | 0.1                    | 0.2               | V    | 2 mA output current                      |

| Input Current per Signal Channel                             | l <sub>iN</sub>  | -10                                | 0.5                    | 10                | μA   | $0 V \le Signal voltage \le V_{DDX}^{1}$ |

| V <sub>DDx</sub> <sup>1</sup> Undervoltage Rising Threshold  | VDDxUV+          | 2.45                               | 2.75                   | 2.95              | V    |                                          |

| V <sub>DDx</sub> <sup>1</sup> Undervoltage Falling Threshold | VDDxUV-          | 2.30                               | 2.60                   | 2.75              | V    |                                          |

| V <sub>DDx</sub> <sup>1</sup> Hysteresis                     | Vddxuvh          |                                    | 0.15                   |                   | V    |                                          |

Notes:

$^1\,V_{\text{DDx}}$  is the side voltage power supply V\_DD, where x = 1 or 2.

## Table 7. Quiescent Supply Current

VDD1 - VGND1 = VDD2 - VGND2 = 3.3VDC±10% or 5VDC±10%, TA=25°C, CL = 0 pF, unless otherwise noted.

| Part    | Symbol                    | Min    | Typ               | Max   | Unit | Test (               | Conditions             |  |

|---------|---------------------------|--------|-------------------|-------|------|----------------------|------------------------|--|

| Part    |                           | IVIIII | Тур               | IVIAX | Onic | Supply voltage       | Input signal           |  |

|         | IDD1(Q) 0.06 0.08 0.10 mA |        | VI=0V for π110E30 |       |      |                      |                        |  |

|         | DD2 (Q)                   | 0.47   | 0.59              | 0.76  | mA   | 5V <sub>DC</sub>     | VI=5V for π110E31      |  |

|         | DD1 (Q)                   | 0.15   | 0.19              | 0.25  | mA   | JVDC                 | VI=5V for π110E30      |  |

| π110E3x | DD2 (Q)                   | 0.44   | 0.55              | 0.72  | mA   |                      | VI=0V for $\pi$ 110E31 |  |

| NIIUE3X | DD1 (Q)                   | 0.06   | 0.08              | 0.10  | mA   |                      | VI=0V for π110E30      |  |

|         | DD2 (Q)                   | 0.46   | 0.58              | 0.75  | mA   | - 3.3V <sub>DC</sub> | VI=3.3V for π110E31    |  |

|         | DD1 (Q)                   | 0.11   | 0.14              | 0.18  | mA   | 5.5V <sub>DC</sub>   | VI=3.3V for π110E30    |  |

|         | DD2 (Q)                   | 0.43   | 0.53              | 0.69  | mA   |                      | VI=0V for $\pi$ 110E31 |  |

## Table 8.Total Supply Current vs. Data Throughput (CL = 0 pF)

VDD1 - VGND1 = VDD2 - VGND2 = 3.3VDC±10% or 5VDC±10%, TA=25°C, CL = 0 pF, unless otherwise noted.

| Part    | Symbol | 150 Kbps |      |      |     | 10 Mbps |      |     | 100 Mbps |      |                           | Supply             |

|---------|--------|----------|------|------|-----|---------|------|-----|----------|------|---------------------------|--------------------|

|         | Symbol | Min      | Тур  | Max  | Min | Тур     | Max  | Min | Тур      | Max  | Unit                      | voltage            |

|         | DD1    |          | 0.12 | 0.18 |     | 0.20    | 0.30 |     | 1.01     | 1.52 | 71 <sup>mA</sup><br>92 mA | 5V <sub>DC</sub>   |

| 44050   | DD2    |          | 0.57 | 0.86 |     | 1.06    | 1.58 |     | 4.48     | 6.71 |                           |                    |

| π110E3x | DD1    |          | 0.10 | 0.15 |     | 0.16    | 0.24 |     | 0.61     | 0.92 |                           | 2.21/              |

|         | IDD2   |          | 0.56 | 0.84 |     | 0.86    | 1.29 |     | 2.93     | 4.39 |                           | 3.3V <sub>DC</sub> |

## INSULATION AND SAFETY RELATED SPECIFICATIONS

Table 9. Insulation Specifications

| Parameter                                        | Symbol                                                                                | Value | Unit                                                                             | Test Conditions/Comments                                                             |

|--------------------------------------------------|---------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |                                                                                       | 3000  | V rms                                                                            | 1-minute duration                                                                    |

| Minimum External Air Gap (Clearance)             | earance) L (CLR) ≥4 mm Measured from input terminals to shortest distance through air |       | Measured from input terminals to output terminals, shortest distance through air |                                                                                      |

| Minimum External Tracking (Creepage)             | L (CRP)                                                                               | ≥4    | mm                                                                               | Measured from input terminals to output terminals, shortest distance path along body |

| Minimum Internal Gap (Internal Clearance)        |                                                                                       | ≥11   | μm                                                                               | Insulation distance through insulation                                               |

| Tracking Resistance (Comparative Tracking Index) | CTI                                                                                   | >400  | V                                                                                | DIN EN 60112 (VDE 0303-11):2010-05                                                   |

| Material Group                                   |                                                                                       | П     |                                                                                  | IEC 60112:2003 + A1:2009                                                             |

## PACKAGE CHARACTERISTICS

Table 10.Package Characteristics

| Parameter                                  | Symbol | Typical<br>Value | Unit | Test Conditions/Comments                  |

|--------------------------------------------|--------|------------------|------|-------------------------------------------|

| Resistance (Input to Output) <sup>1</sup>  | Rio    | 1011             | Ω    |                                           |

| Capacitance (Input to Output) <sup>1</sup> | Сю     | 0.6              | pF   | @1MHz                                     |

| Input Capacitance <sup>2</sup>             | Cı     | 3.0              | pF   | @1MHz                                     |

| IC Junction to Ambient Thermal             | θJA    | 100              | °C/W | Thermocouple located at center of package |

| Resistance                                 | DJA    | 100              | C/ W | underside                                 |

Notes:

<sup>1</sup>The device is considered a 2-terminal device; SOIC-8 Pin 1 - Pin 4 are shorted together as the one terminal, and SOIC-8 Pin 5 - Pin 8 are shorted together as the other terminal.

<sup>2</sup>Testing from the input signal pin to ground.

## **REGULATORY INFORMATION**

See Table 11 for details regarding recommended maximum working voltages for specific cross isolation waveforms and insulation levels. Table 11.Regulatory

| Regulatory  | π110E3x                                                                          |

|-------------|----------------------------------------------------------------------------------|

|             | Recognized under UL 1577                                                         |

|             | Component Recognition Program <sup>1</sup>                                       |

| UL          | Single Protection, 3000 V rms Isolation Voltage                                  |

|             | File (E494497)                                                                   |

|             | DIN VDE V 0884-11:2017-01 <sup>2</sup>                                           |

| VDE         | Basic insulation, V <sub>IORM</sub> = 565V peak, V <sub>IOSM</sub> = 3615 V peak |

|             | File (40053041)                                                                  |

|             | Certified under CQC11-471543-2012, GB4943.1-2011                                 |

| <b>60</b> 5 | Basic insulation at 500 V rms (707 V peak) working voltage                       |

| CQC         | Reinforced insulation at 250 V rms (353 V peak)                                  |

|             | NB SOIC-8 File (CQC20001260211)                                                  |

Notes:

<sup>1</sup> In accordance with UL 1577, each  $\pi$ 110E3x is proof tested by applying an insulation test voltage  $\geq$  3600 V rms for 1 sec

<sup>2</sup> In accordance with DIN V VDE V 0884-11, each  $\pi$ 110E3x is proof tested by applying an insulation test voltage  $\geq$  848 V peak for 1 sec (partial discharge detection limit = 5 pC).

## DIN V VDE V 0884-11 (VDE V 0884-11) INSULATION CHARACTERISTICS

Table 12.VDE Insulation Characteristics

| Description                                   | Test Conditions/Comments                                                                                           | Symbol              | Characteristic | Unit  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------|----------------|-------|

| Installation Classification per DIN VDE 0110  |                                                                                                                    |                     |                |       |

| For Rated Mains Voltage ≤ 150 V rms           |                                                                                                                    |                     | I to IV        |       |

| For Rated Mains Voltage ≤ 300 V rms           |                                                                                                                    |                     | l to III       |       |

| For Rated Mains Voltage ≤ 400 V rms           |                                                                                                                    |                     | l to III       |       |

| Climatic Classification                       |                                                                                                                    |                     | 40/105/21      |       |

| Pollution Degree per DIN VDE 0110, Table 1    |                                                                                                                    |                     | 2              |       |

| Maximum repetitive peak isolation voltage     |                                                                                                                    | VIORM               | 565            | Vpeak |

| Input to Output Test Voltage, Method B1       | $V_{IORM} \times 1.5 = V_{pd (m)}, 100\%$<br>production test, $t_{ini} = t_m = 1$ sec,<br>partial discharge < 5 pC | V <sub>pd (m)</sub> | 848            | Vpeak |

| Input to Output Test Voltage, Method A        |                                                                                                                    | Vpd (m)             |                |       |

| After Environmental Tests Subgroup 1          | $V_{IORM} \times 1.2 = V_{pd (m)}, t_{ini} = 60 \text{ sec, } t_m$<br>= 10 sec, partial discharge < 5 pC           | Vpd (m)             | 678            | Vpeak |

| After Input and/or Safety Test Subgroup 2 and | $V_{IORM} \times 1.2 = V_{pd (m)}, t_{ini} = 60 \text{ sec, } t_m$                                                 |                     | 678            | Vpeak |

| Subgroup 3                                    | = 10 sec, partial discharge < 5 pC                                                                                 |                     | 078            | vреак |

| Highest Allowable Overvoltage                 |                                                                                                                    | VIOTM               | 4200           | Vpeak |

Data Sheet

| Description                       | Test Conditions/Comments                                                                             | Symbol | Characteristic | Unit  |  |

|-----------------------------------|------------------------------------------------------------------------------------------------------|--------|----------------|-------|--|

| Surge Isolation Voltage Basic     | Basic insulation, 1.2/50 μs<br>combination wave, VTEST = 1.3 ×<br>VIOSM (qualification) <sup>1</sup> | Viosm  | 3615           | Vpeak |  |

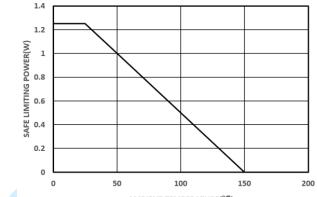

| Safety Limiting Values            | Maximum value allowed in the event of a failure (see <i>Figure 4</i> )                               |        |                |       |  |

| Maximum Safety Temperature        |                                                                                                      | Ts     | 150            | °C    |  |

| Maximum Power Dissipation at 25°C |                                                                                                      | Ps     | 1.25           | W     |  |

| Insulation Resistance at Ts       | V <sub>IO</sub> = 500 V                                                                              | Rs     | >109           | Ω     |  |

Notes:

<sup>1</sup>In accordance with DIN V VDE V 0884-11,  $\pi$ 1xxx3x is proof tested by applying a surge isolation voltage 4700 V.

## Typical Thermal Characteristic

AMBIENT TEMPERATURE(°C)

Figure 4.Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per VDE

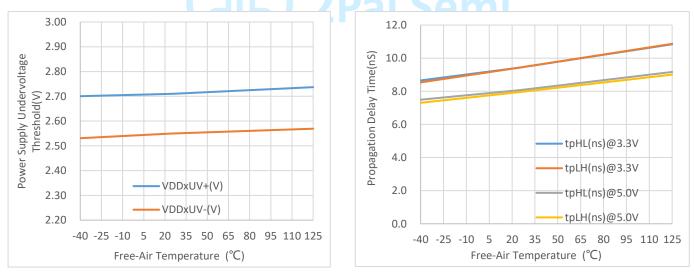

Figure 5.UVLO vs. Free-Air Temperature

Figure 6. Propagation Delay Time vs. Free-Air Temperature

# **Data Sheet**

## Timing test information

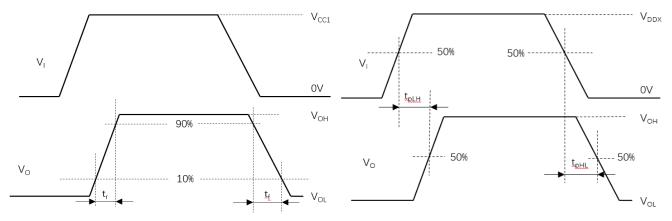

Figure 7.Transition time waveform measurement

Figure 8. Propagation delay time waveform measurement

## **APPLICATIONS INFORMATION**

## **OVERVIEW**

The  $\pi 1 \times \times \times \times a$  are 2PaiSemi digital isolators product family based on 2PaiSEMI unique *iDivider*<sup>®</sup> technology. Intelligent voltage **Divider** technology (*iDivider*<sup>®</sup> technology) is a new generation digital isolator technology invented by 2PaiSEMI. It uses the principle of capacitor voltage divider to transmit signal directly cross the isolator capacitor without signal modulation and demodulation. Compare to the traditional Opto-couple technology, icoupler technology, OOK technology, *iDivider*<sup>®</sup> is a more essential and concise isolation signal transmit technology which leads to greatly simplification on circuit design and therefore significantly improves device performance, such as lower power consumption, faster speed, enhanced anti-interference ability, lower noise.

By using maturated standard semiconductor CMOS technology and the innovative *iDivider*<sup>®</sup> design, these isolation components provide outstanding performance characteristics and reliability superior to alternatives such as optocoupler devices and other integrated isolators. The  $\pi 1 \times \times \times \times$  isolator data channels are independent and are available in a variety of configurations with a withstand voltage rating of 1.5 kV rms to 6.0 kV rms and the data rate from DC up to 600Mbps (see the Ordering Guide).

The  $\pi$ 110E3x are the outstanding 200Mbps single-channel digital isolators with the enhanced ESD capability. the devices transmit data across an isolation barrier by layers of silicon dioxide isolation.

The devices operate with the supply voltage on either side ranging from 3.0 V to 5.5 V, offering voltage translation of 3.3 V, and 5 V logic. The  $\pi$ 110E3x have very low propagation delay and high speed. The input/output design techniques allow logic and supply voltages over a wide range from 3.0 V to 5.5 V, offering voltage translation of 3.3 V, and 5 V logic. The architecture is designed for high common-mode transient immunity and high immunity to electrical noise and magnetic interference.

See the Ordering Guide for the model numbers that have the failsafe output state of low or high.

## PCB LAYOUT

The low-ESR ceramic bypass capacitors must be connected between  $V_{DD1}$  and  $GND_1$  and between  $V_{DD2}$  and  $GND_2$ . The bypass capacitors are placed on the PCB as close to the isolator device as possible. The recommended bypass capacitor value is between 0.1  $\mu F$  and 10  $\mu F$ . To enhance the robustness of a design, the user may also include resistors (50–300  $\Omega$ ) in series with the inputs and outputs if the system is excessively noisy.

Avoid reducing the isolation capability, Keep the space underneath the isolator device free from metal such as planes, pads, traces and vias.

To minimize the impedance of the signal return loop, keep the solid ground plane directly underneath the high-speed signal path, the closer the better. The return path will couple between the nearest ground plane to the signal path. Keep suitable trace width for controlled impedance transmission lines interconnect.

To reduce the rise time degradation, keep the length of input/output signal traces as short as possible, and route low inductance loop for the signal path and It's return path.

Figure 9. Recommended Printed Circuit Board Layout

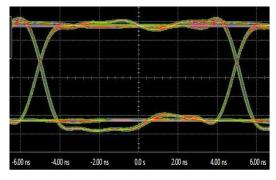

#### JITTER MEASUREMENT

The eye diagram shown in the figure below provides the jitter measurement result for the  $\pi$ 110E3x. The Keysight 81160A pulse function arbitrary generator works as the data source for the  $\pi$ 110E3x, which generates 100Mbps pseudo random bit sequence (PRBS). The Keysight DSOS104A digital storage oscilloscope captures the  $\pi$ 110E3x output waveform and recoveries the eye diagram with the SDA tools and eye diagram analysis tools. The result shows a typical measurement jitter data.

## **CMTI MEASUREMENT**

Figure 11.Common-mode transient immunity (CMTI) measurement

To measure the Common-Mode Transient Immunity (CMTI) of  $\pi 1xxxxx$  isolator under specified common-mode pulse magnitude (VCM) and specified slew rate of the common-mode pulse (dVCM/dt) and other specified test or ambient conditions, The common-mode pulse generator (G1) will be capable of providing fast rise and fall pulses of specified magnitude and duration of the common-mode pulse (VCM), such that the maximum common-mode slew rates (dVCM/dt) can be applied to  $\pi 1xxxxx$  isolator coupler under measurement. The common-mode pulse is applied between one side ground GND1 and the other side ground GND2 of  $\pi 1xxxxx$  isolator, and shall be capable of providing positive transients as well as negative transients.

## Data Sheet

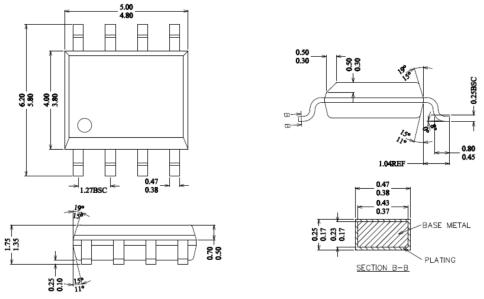

## **OUTLINE DIMENSIONS**

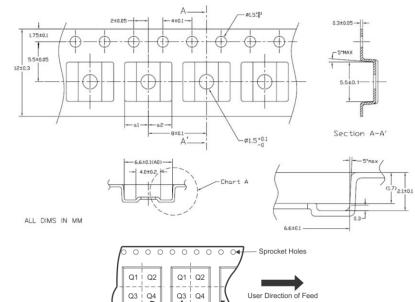

Figure 12. 8-Lead Narrow Body SOIC [NB SOIC-8] Package-dimension unit(mm)

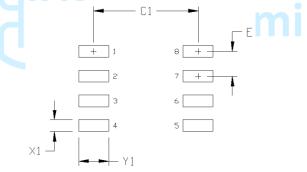

## Land Patterns

8-Lead Narrow Body SOIC [NB SOIC-8]

The figure below illustrates the recommended land pattern details for the  $\pi$ 1xxxxx in an 8-pin narrow-body SOIC. The table below lists the values for the dimensions shown in the illustration.

#### Figure 13.8-Lead Narrow Body SOIC [NB SOIC-8] Land Pattern

#### Table 13.8-Lead Narrow Body SOIC Land Pattern Dimensions

| Dimension | Feature            | Parameter | Unit |  |

|-----------|--------------------|-----------|------|--|

| C1        | Pad column spacing | 5.40      | mm   |  |

| E         | Pad row pitch      | 1.27      | mm   |  |

| X1        | Pad width          | 0.60      | mm   |  |

| Y1        | Pad length         | 1.55      | mm   |  |

Note:

1. This land pattern design is based on IPC -7351.

2.All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

# **Top Marking**

| Line 1               | Product name                              |  |

|----------------------|-------------------------------------------|--|

| Line 2               | YY = Work Year                            |  |

|                      | WW = Work Week                            |  |

|                      | ZZ=Manufacturing code from assembly house |  |

| Line 3               | XXXX, no special meaning                  |  |

| Figure 14.Top Making |                                           |  |

## **REEL INFORMATION**

Note: The Pin 1of the chip is in the quadrant Q1 Figure 15.NB SOIC-8 Reel Information—*dimension unit(mm)*

Pocket Quadrants

## **ORDERING GUIDE**

| Model<br>Name <sup>1</sup> | Temperature<br>Range | No. of Inputs,<br>V <sub>DD1</sub> Side | No. of Inputs,<br>V <sub>DD2</sub> Side | Isolation Rating<br>(kV rms) | Fail-Safe<br>Output State | Package   | MSL<br>Peak Temp <sup>2</sup> | MOQ/<br>Quantity<br>per reel <sup>3</sup> |

|----------------------------|----------------------|-----------------------------------------|-----------------------------------------|------------------------------|---------------------------|-----------|-------------------------------|-------------------------------------------|

| π110E31                    | -40~125°C            | 1                                       | 0                                       | 3                            | High                      | NB SOIC-8 | Level-3-260C-168 HR           | 4000                                      |

| π110E30                    | –40~125°C            | 1                                       | 0                                       | 3                            | Low                       | NB SOIC-8 | Level-3-260C-168 HR           | 4000                                      |

Note:

$^{\rm 1.}$  Pai1xxxxx is equals to  $\pi 1xxxxx$  in the customer BOM

<sup>2</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>3.</sup> MOQ, minimum ordering quantity.

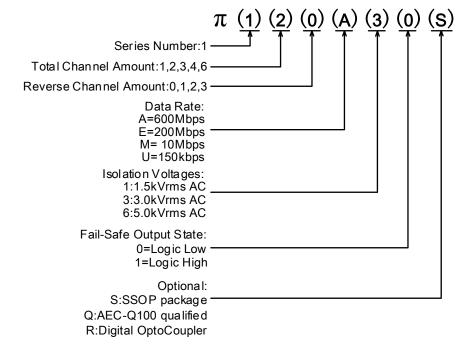

## PART NUMBER NAMED RULE

Notes:Pai1xxxxx is equals to  $\pi$ 1xxxxx in the customer BOM

Figure 16. Part Number Named Rule

# IMPORTANT NOTICE AND DISCLAIMER

2Pai semi intends to provide customers with the latest, accurate, and in-depth documentation. However, no responsibility is assumed by 2Pai semi for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Characterization data, available modules, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. 2Pai semi reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. 2Pai semi shall have no liability for the consequences of use of the information supplied herein.

Trademarks and registered trademarks are the property of their respective owners. This document does not imply, or express copyright licenses granted hereunder to design or fabricate any integrated circuits.

Room 307-309, No.22, Boxia Road, Pudong New District, Shanghai, 201203, China 021-50850681

2Pai Semiconductor Co., Limited. All rights reserved.

http://www.rpsemi.com/

# **REVISION HISTORY**

| Revision | Date       | Page        | Change Record                                                                                                                                                                                 |  |  |  |

|----------|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.0      | 2018/09/17 | All         | Initial version                                                                                                                                                                               |  |  |  |

| 1.1      | 2018/11/28 | P11         | Changed the recommended bypass capacitor value.                                                                                                                                               |  |  |  |

| 1.2      | 2019/09/08 | Page1       | Changed the contact address.<br>Add <i>iDivider</i> technology description in General Description.<br>Changed propagation delay time, CMTI and HBM ESD.<br>Added WB SOIC-16 Lead information. |  |  |  |

| 1.3      | 2019/12/20 | Page1,11,14 | Changed description of $\pi$ 1xxx6x.                                                                                                                                                          |  |  |  |

| 1.4      | 2020/02/16 | Page1       | Changed propagation delay time.                                                                                                                                                               |  |  |  |

| 1.5      | 2020/02/25 | Page5       | Changed Pulse Width Distortion.                                                                                                                                                               |  |  |  |

| 1.6      | 2020/03/16 | Page6       | Changed VDDx Undervoltage Threshold and Regulatory Information.<br>Added information of Land Patterns and Top Marking                                                                         |  |  |  |

| 1.7      | 2020/04/16 | Page12      | Optimize description and format to make it consistent with the Chinese version.                                                                                                               |  |  |  |

| 1.8      | 2021/05/17 | Page 11     | Changed part number named rule                                                                                                                                                                |  |  |  |