# F-TLV700 Series

### Features

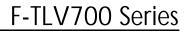

- Low Dropout Voltage:

- ♦ 170mV at 200mA

- 230mV at 300mA

- Maximum Output Current: 300mA

- Input Voltage Range: 2.1V to 5.5V

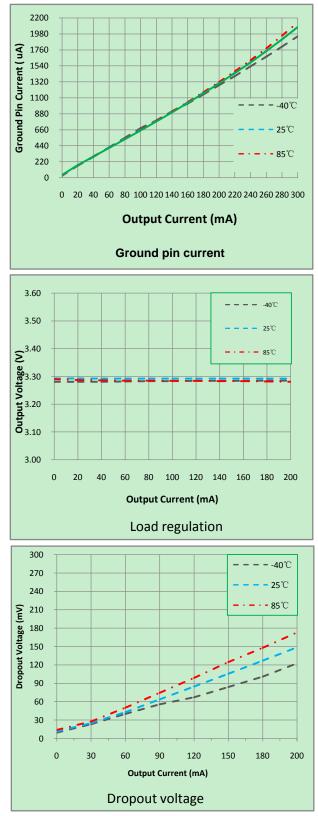

- ±2% Accuracy Overall Operating Conditions

- Low Quiescent and Shutdown Current

- Foldback Current Limit and Overheat Protection

- Stable with Effective Capacitance of 1 µF

- Soft-start Limits Input Current Surge During Enable

- Available in Fixed-Output Voltages 1.8V/2.8V/3.0V/3.3V

- Temperature range: -40°C ~ +85°C

- Available in 3-mm × 3-mm SOT23-5 package and SC70-5 package

## Applications

- POS

- Handheld Devices Including Medical Handhelds

- U-Key

- Lower Cost Industrial and Instrumentation

- Battery Device

## Description

### 300mA, Low Iq, LDO with foldback current

TLV700 series product is a high performance and low dropout linear regulator. Current output capability is 300mA. TLV700 series product support low quiescent current and high-PSRR, especially for high frequency. TLV700 series can be stable with output capacitance of 1µF to 10µF with ESR of up to 100m $\Omega$ .

The TLV700 series have a high PSRR at high frequency and PSRR can be about 70dB at 2M frequency point. This feature makes TLV700 series very suitable for power-sensitive applications with high noise from front stage power supply. When coupled with a no load quiescent current of  $35\mu$ A (typical) and 0.1 $\mu$ A shutdown current, the TLV700 series is an ideal choice for portable or wireless equipment. Current-limit and thermal overload protection circuits prevent damage under these conditions. The TLV700 series also includes an internal pull-down resistor on the EN input.

The TLV700 series comes in many fixed voltage options with  $\pm 2\%$  output voltage accuracy over temperature, line and load. Other output voltage options are available on request.

The TLV700 series is guaranteed over the temperature range of -40°C to +85°C. The TLV700 series of LDOs are available in 3-mm\*3-mm SOT23-5 package and SC70-5 package.

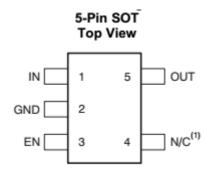

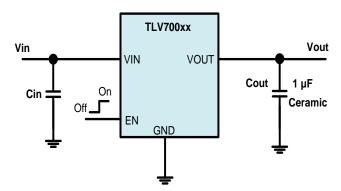

# **Typical Application Circuit**

## **Absolute Maximum Ratings\***

|                        |                        | Min     | Мах     | Unit |

|------------------------|------------------------|---------|---------|------|

|                        | Vin                    | -0.3    | 7       | V    |

| Voltage                | Ven                    | -0.3    | 7       | V    |

|                        | Vout                   | -0.3    | 7       | V    |

| Maximum output current | lout                   | Interna | limited | mA   |

| Temperature            | Operating junction, TJ | -55     | 150     | °C   |

|                        | Storage, Tstg          | -55     | 150     | °C   |

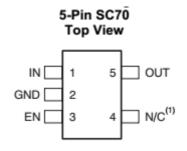

# Pin Configuration (Top View)

|      | Р   | IN  |        | 1/0 | Departmention                                                                                                                   |  |

|------|-----|-----|--------|-----|---------------------------------------------------------------------------------------------------------------------------------|--|

| Name | SOT | DFN | SC70-5 | I/O | Description                                                                                                                     |  |

| IN   | 1   | 4   | 1      | I   | Input voltage pin. Bypass $V_{\text{IN}}$ to GND with a $1\mu\text{F}$ or greater capacitor.                                    |  |

| OUT  | 5   | 1   | 5      | 0   | Regulated output voltage. Bypass $V_{\mbox{\scriptsize OUT}}$ to GND with a $1\mu F$ or greater capacitor.                      |  |

| EN   | 3   | 3   | 3      | I   | Drive EN high to turn on the regulator; drive EN low to turn off the regulator. For automatic startup, connect EN to $V_{IN}$ . |  |

| NC   | 4   | -   | 4      | -   | No connection. This pin can be tied to ground to improve thermal dissipation.                                                   |  |

| GND  | 2   | 2   | 2      | -   | GND is the connection to system ground. Connect to PCB Ground plane                                                             |  |

# **ESD** Rating

|                                      |                                                                              | Value   | Units |

|--------------------------------------|------------------------------------------------------------------------------|---------|-------|

| V(ESD)<br>Electrostatic<br>discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins                 | +/-8000 | V     |

|                                      | Charged device model (CDM), per JEDEC specification JESD22-C101, V all pins( | +/-2000 | V     |

# **Recommended Operating Conditions**

|      | Min | Nom | Мах | Units |

|------|-----|-----|-----|-------|

| Vin  | 2.1 |     | 5.5 | V     |

| lout | 0   |     | 300 | mA    |

### **Thermal Information**

| THERMAL METRIC                                         | TLV700  | Unit |

|--------------------------------------------------------|---------|------|

|                                                        | SOT23-5 |      |

| R0JA Junction-to-ambient thermal resistance            | 280     |      |

| R0JC(top) Junction-to-case (top) thermal resistance    | 61.9    |      |

| R0JB Junction-to-board thermal resistance              | 54      | °C/W |

| ψJT Junction-to-top characterization parameter         | 0.8     |      |

| wJB Junction-to-board characterization parameter       | 53.4    |      |

| R0JC(bot) Junction-to-case (bottom) thermal resistance | n/a     |      |

### **Order information**

| Model Name | Class | Vo   | Order Number** | Package | Transport Media, Quantity | Marking Information |

|------------|-------|------|----------------|---------|---------------------------|---------------------|

| TLV70018   | Fixed | 1.8V | F-TLV70018DDCR | SOT23-5 | Tape and Reel, 3,000      |                     |

| TLV70028   | Fixed | 2.8V | F-TLV70028DDCR | SOT23-5 | Tape and Reel, 3,000      |                     |

| TLV70030   | Fixed | 3.0V | F-TLV70030DDCR | SOT23-5 | Tape and Reel, 3,000      |                     |

| TLV70033   | Fixed | 3.3V | F-TLV70033DDCR | SOT23-5 | Tape and Reel, 3,000      |                     |

| TLV70033   | Fixed | 3.3V | F-TLV70033DCKR | SOC70-5 | Tape and Reel, 3,000      |                     |

## **Electrical Characteristics**

At VIN = VOUT (Typ) + 0.3 V or 2.0 V (whichever is greater); IOUT = 10 mA, VEN = 0.9 V, COUT = 1.0  $\mu$ F, and TJ = -40°C to +125°C, unless otherwise noted. Typical values are at TJ = +25°C.

| SYMBOL                                         | PARAMETER                       | TEST CONDITIONS                                                                                                                                                         | MIN | ТҮР  | MAX             | UNITS |

|------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----------------|-------|

| V <sub>IN</sub>                                | Input Voltage Range             |                                                                                                                                                                         | 2.1 |      | 5.5             | V     |

| Vo                                             | DC output accuracy              | –40°C ≤ T <sub>J</sub> ≤ +125°C                                                                                                                                         | -2  |      | +2              | %     |

| $\Delta V_{\text{IN}} / \Delta V_{\text{OUT}}$ | Line Regulation                 | $\label{eq:Vout(NOM)} \begin{split} V_{\text{OUT(NOM)}} + 0.3 \ V \leq V_{\text{IN}} \leq 5.5 \ \text{V}, \\ I_{\text{OUT}} = 10 \ \text{mA} \end{split}$               |     | 1.5  |                 | mV    |

| $\Delta V_{\text{IN}} / \Delta I_{\text{OUT}}$ | Load Regulation                 | 0 mA ≤ I <sub>OUT</sub> ≤ 300 mA                                                                                                                                        |     | 1    | 15              | mV    |

|                                                |                                 | Vin = Vout(nom), lout = 100 mA,                                                                                                                                         |     | 88   |                 | mV    |

| $\Delta V_{DO}$                                | Dropout Voltage (Note 2)        | Vin = Vout (nom), lout = 200 mA                                                                                                                                         |     | 170  |                 | mV    |

|                                                |                                 | Vin = Vout (nom), lout = 300 mA                                                                                                                                         |     | 230  |                 | mV    |

| I <sub>CL</sub>                                | Output Current Limit            | $V_{OUT} = 0.9 \times V_{OUT(NOM)}$                                                                                                                                     |     | 500  |                 | mA    |

|                                                |                                 | $V_{EN} \leq 0.4 \text{ V}, V_{IN} = 2.0 \text{ V}$                                                                                                                     |     | 400  |                 | nA    |

| I <sub>SHDN</sub>                              | Shutdown Current                | $V_{EN} \le 0.4 \text{ V}, 2.0 \text{ V} \le V_{IN} \le 4.5 \text{ V}$                                                                                                  |     | 1    |                 | μA    |

|                                                |                                 | I <sub>OUT</sub> = 0mA                                                                                                                                                  |     | 35   |                 | μA    |

| I <sub>GND</sub>                               | Quiescent Current               | I <sub>OUT</sub> = 300 mA, V <sub>IN</sub> = V <sub>OUT</sub> + 0.5 V                                                                                                   |     | 1000 |                 | μA    |

| PSRR                                           | Power Supply Rejection<br>Ratio | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 4.3 \ \text{V}, \ V_{\text{OUT}} = 3.3 \ \text{V}, \\ I_{\text{OUT}} = 10 \ \text{mA}, \ f = 1 \text{KHz} \end{array}$ |     | 55   |                 | dB    |

| t <sub>STR</sub>                               | Startup time (Note 3)           | $C_{OUT}$ = 1.0 µF, I <sub>OUT</sub> = 300mA                                                                                                                            |     | 100  |                 | μS    |

| V <sub>EN(HI)</sub>                            | Enable pin high (enabled)       |                                                                                                                                                                         | 0.6 |      | V <sub>IN</sub> | V     |

| V <sub>EN(LO)</sub>                            | Enable pin low (disabled)       |                                                                                                                                                                         | 0   |      | 0.45            | V     |

| I <sub>EN</sub>                                | Enable pin current              | V <sub>IN</sub> = V <sub>EN</sub> = 5.5 V                                                                                                                               |     | 0.03 |                 | μA    |

| UVLO                                           | Under voltage lockout           | V <sub>IN</sub> rising                                                                                                                                                  |     | 1.9  |                 | V     |

| T <sub>SD</sub>                                | Thermal shutdown temperature    | Shutdown, temperature increasing                                                                                                                                        |     | 170  |                 | °C    |

| т                                              | Operating junction              | Reset, temperature decreasing                                                                                                                                           |     | 145  |                 | °C    |

| TJ                                             | temperature                     |                                                                                                                                                                         | -40 |      | +125            | °C    |

**Note 1:** The TLV700 series regulators are tested and specified under pulse load conditions such that TJ  $\approx$  TA. The TLV700 series is 100% production tested at TA = 25°C. Performance at -40°C and 125°C is assured by design, characterization and correlation with statistical process controls.

**Note 2:** Dropout voltage is the minimum input to output voltage differential needed to maintain regulation at a specified output current. In dropout, the output voltage will be equal to: VIN – Vdropout.

Note 3: Startup time = time from EN assertion to 0.98 × VOUT (NOM)

## **Typical Characteristics**

Over operating temperature range (TJ =  $-40^{\circ}$ C to  $+125^{\circ}$ C), VIN = VOUT (nom) + 0.5 V or 2 V, whichever is greater; IOUT = 10 mA,VEN = VIN, COUT = 1  $\mu$ F, unless otherwise noted. Typical values are at TJ =  $25^{\circ}$ C

### Overview

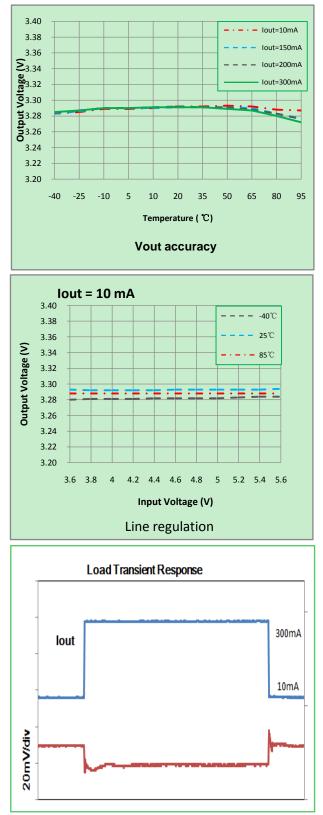

The TLV700 series is a high PSRR, low quiescent current, low dropout linear regulator that operates from 2.1 V to 5.5 V and can provide up to 300mA output current. The TLV700 series consumes a low 35µA of quiescent current (typical). Shutdown currentconsumption is typically 0.1µA.

Internally, the TLV700 series consists of a reference, an error amplifier, a feedback voltage divider, and a PMOS pass transistor. Output current is delivered via the PMOS pass device, which is controlled by the error amplifier. The error amplifier compares thereference voltage with the feedback voltage from the output and amplifies the difference. If the feedback voltage is lower than thereference voltage, the gate of the PMOS device is pulled lower, allowing more current to pass and increasing the output voltage. If the feedback voltage is higher than the reference voltage, the gate of the PMOS device is pulled lower, allowing more current to pass and increasing the scurrent to pass and decreasing the output voltage.

The TLV700 series is available in all output voltage options, ranging from 0.8 V to 5.0 V

### **Functional block diagram**

### **Features description**

### **Enable Feature**

The enable pin (EN) is active high. The device is enabled when the voltage at the EN pin goes above 0.6V. This relatively lower voltage value required to turn the LDO on can be exploited to power the LDO with a GPIO of recent processors whose GPIO logic 1 voltage level is lower than traditional microcontrollers. The device is turned off when the EN pin is held at less than 0.4V. When shutdown capability is not required, EN can be connected to the IN pin.

### **Current Limit Protection**

The TLV700 series has an internal foldback current limit that helps to protect the regulator during fault conditions. The current supplied by the device is gradually throttled down as the output voltage decreases. When the output is shorted, the LDO supplies a typical current of 90 mA. Output voltage is not regulated when the device is in current limit, and is VOUT = ILIMIT × RLOAD. The advantage of foldback current limit is that the ILIMIT value is less than the fixed current limit. Therefore, the power that the PMOS pass transistor dissipates [(VIN – VOUT) × ILIMIT] is much less.

The TLV700 series PMOS pass element has a built-in body diode that conducts current when the voltage at OUT exceeds the voltage at IN. This current is not limited, so if extended reverse voltage operation is anticipated, external limiting to 5% of the rated output current is recommended.

### **Output Capacitance and Transient Response**

The TLV700 series is designed for operation with small, space-saving ceramic capacitors, but it can function with most commonly used capacitors as long as care is taken with regard to the effective series resistance (ESR) value. The ESR of the output capacitor affects the stability of the LDO control loop. A minimum of  $1\mu$ F capacitance with an ESR of 100 m $\Omega$  or less is recommended to ensure the stability of the TLV700 series. For output voltage stable, we high recommend that the output capacitance should be near to the voltage output pin.Transient response to changes in load current is also affected by output capacitance. Using a larger value of output capacitance improves the transient response of the TLV700 series to large changes in load current.

### Under voltage Lockout (UVLO)

The TLV700 series uses an under voltage lockout circuit (UVLO = 1.9 V) to keep the output shut off until the internal circuitry operates properly.

#### **Input Bypass Capacitor**

Connecting a  $1\mu$ F capacitor from VIN to GND reduces the circuit sensitivity to the PCB layout, especially when long input traces or high source impedance are encountered. If output capacitance greater than  $1\mu$ F is required, the input capacitor should be increased to match it.

#### **Thermal Fault Protection**

In the event that the die temperature exceeds typically +170°C, the output of the LDO will shut down until the die temperature cools down to typically +145°C, the output circuitry is again enabled. The level of power dissipated, combined with the ambient temperature and the thermal impedance of the package, will determine if the junction temperature exceeds the thermal shutdown temperature. Also see the section on "Power Dissipation".

#### **Power Dissipation**

The junction temperature must not exceed the range specified in "Recommended Operating Conditions" on page 3. The power dissipation can be calculated using below Equation:

#### PD = (VIN - VOUT) X IOUT + VIN X IGND

The maximum allowable junction temperature, TJ(MAX) and the maximum expected ambient temperature, TA(MAX) will determine the maximum allowable junction temperature rise ( $\Delta$ TJ), as shown in below Equation:

#### $\Delta T_J = T_{J(MAX)} - T_{A(MAX)}$

To calculate the maximum ambient operating temperature, use the junction-to-ambient thermal resistance (0JA), as shown in below Equation:

#### $T_{J(MAX)} = P_{D(MAX)} \times \theta_{JA} + T_A$

### **Application and Implementation**

**NOTE** Information in the following applications sections is not part of the FLH's component specification and FLH does not warrant its accuracy or completeness. FLH's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### **Typical Application Circuit**

The input and output capcitance requirement FLH recommends using 1 $\mu$ F X5R- and X7R-type ceramic capacitors because these capacitors have minimal variation in value and equivalent series resistance (ESR) over temperature. However, the TLV700 series is designed to be stable with an effective capacitance of 1 $\mu$ F or larger at the output. Thus, the device is stable with capacitors of other dielectric types as well, as long as the effective capacitance under operating bias voltage and temperature is greater than 1 $\mu$ F. This effective capacitance refers to the capacitance that the LDO sees under operating bias voltage and temperature conditions; that is, the capacitance after taking both bias voltage and temperature derating into consideration. In addition to allowing the use of cheaper dielectrics, this capability of being stable with 1 $\mu$ F effective capacitance also enables the use of smaller footprint capacitors that have higher derating in size- and space-constrained applications.

Using a 1 $\mu$ F rated capacitor at the output of the LDO does not ensure stability because the effective capacitance under the specified operating conditions must not be less than 1 $\mu$ F. Maximum ESR should be less than 100 m $\Omega$ .

Although an input capacitor is not required for stability, it is good analog design practice to connect a  $0.1\mu$ F to  $10\mu$ F, low ESR capacitor across the IN pin and GND in of the regulator. This capacitor counteracts reactive input sources and improves transient response, noise rejection, and ripple rejection. A higher-value capacitor may be necessary if large, fast rise-time load transients are anticipated, or if the device is not located close to the power source. If source impedance is more than  $2\Omega$ , a  $1\mu$ F input capacitor may be necessary to ensure stability.

#### Layout requirement

Input and output capacitors should be placed as close to the device pins as possible. To improve AC performance such as PSRR, output noise, and transient response, FLH recommends designing the printed-circuit boards with separate ground planes for VIN and VOUT, with the ground plane connected only at the GND pin of the device. In addition, the ground connection for the output capacitor should be connected directly to the GND pin of the device. High ESR capacitors may degrade PSRR performance.

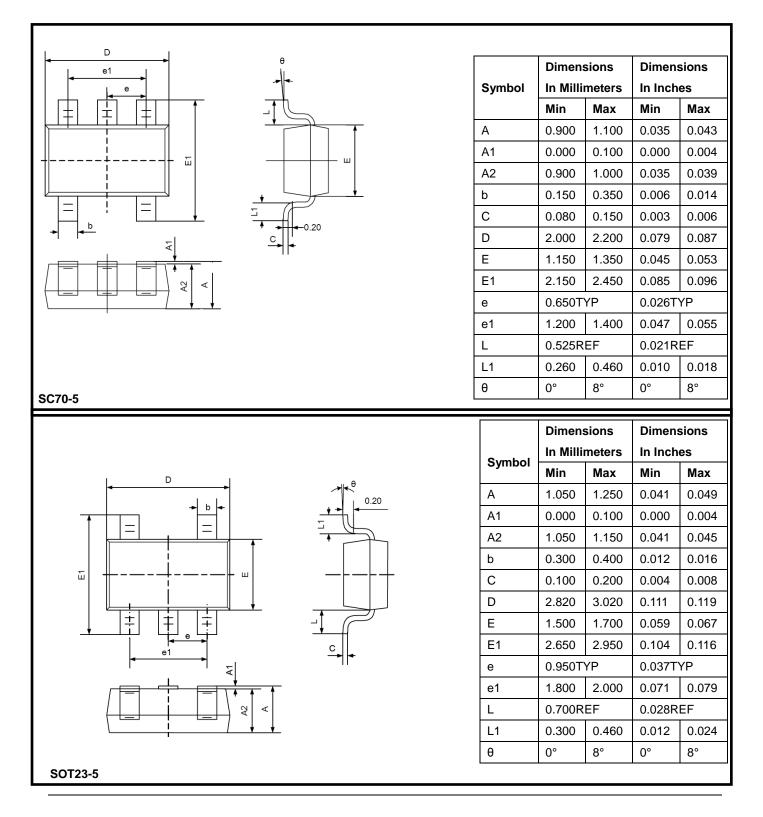

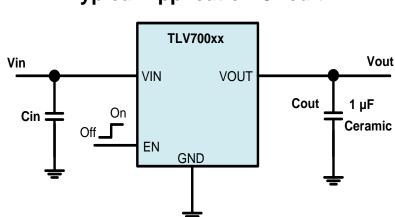

### **Package Outline Dimensions**