# **Application Note: SY6018B**

### **Analog Class-D Audio IC**

### **General Description**

The SY6018B is a Class-D audio power amplifier with analog input and high-power efficiency for driving bridged-tied mono speaker with up to  $60W/4\Omega$ . The high efficiency of the SY6018B eliminates the need for an external heat sink when playing music.

The SY6018B advanced oscillator/PLL circuit employs a multiple switching frequency option to avoid AM interference, this is achieved together with an option of Master and Slave synchronization, making it possible to synchronize multiple devices.

The SY6018B is fully protected against faults including short circuit, over temperature, DC error, under voltage and over voltage. The short circuit, over temperature and DC error protection includes an auto-recovery feature. The under voltage and over voltage protection with hysteresis can be self-cleared.

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6018BOEC      | OFN5x5-32    |      |

#### **Features**

- 60W into a 4Ω Load @ 10% THD+N from a 24V Supply

- Wide Supply Voltage Range from 5.6V to 26 V

- Differential and Single-ended Inputs

- Internal Feedback Control with High PSRR

- High Efficient Class-D Operation Eliminates Need for Heat Sinks

- AM Avoidance

- Master/Slave Mode Synchronization

- Four Fixed-gain Controlled: 20dB, 26dB, 32dB and 36dB

- Selectable BD Mode and 1SPW Mode Modulation

- Integrated Protection Circuits Including Over Voltage, Under Voltage, Over Temperature, DC Error, and Short Circuit

- Comprehensive Click and Pop Suppression

- Space-Saving Surface Mount 32-Pin QFN 5mmx5mm Package

### **Applications**

- Powered Speakers

- Music Instruments

- Boom Box

- Consumer Audio Applications

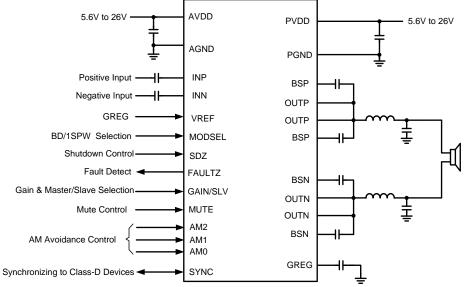

## **Typical Application**

### Pin out (Top View)

Top Mark: ENAxyz (device code: ENA, x=year code, y=week code, z= lot number code)

| Name     | No.             | Description                                                                             |  |

|----------|-----------------|-----------------------------------------------------------------------------------------|--|

| VREF     | 1               | Internal reference pin. Connect to GREG directly.                                       |  |

| GREG     | 2               | Gate drive supply. Nominal voltage is 3.4V.                                             |  |

| GAIN/SLV | 3               | Gain & Master/Slave mode selection depending on voltage divider from GREG to GND.       |  |

| AGND     | 4               | Analog Ground.                                                                          |  |

| NC       | 5               | Not Connected.                                                                          |  |

| NC       | 6               | Not Connected.                                                                          |  |

| MUTE     | 7               | Mute pin (high=mute, low=unmute), TTL logic levels with compliance to AVDD.             |  |

| AM2      | 8               | AM avoidance frequency selection.                                                       |  |

| AM1      | 9               | AM avoidance frequency selection.                                                       |  |

| AM0      | 10              | AM avoidance frequency selection.                                                       |  |

| SYNC     | 11              | Clock input/output for synchronizing other Class-D devices. Determined by Gain/SLV pin. |  |

| AVDD     | 12              | Analog power supply. Not internally connected to PVDD.                                  |  |

| PVDD     | 13,14,27,<br>28 | Power supply.                                                                           |  |

| BSN      | 15,19           | Bootstrap for negative high-side FET.                                                   |  |

| OUTN     | 16,18           | H-bridge negative output.                                                               |  |

| PGND     | 17,21,24        | Power Ground.                                                                           |  |

| MODSEL   | 20              | Mode selection (low=BD, high=1SPW), TTL logic levels with compliance to AVDD            |  |

| BSP      | 22,26           | Bootstrap for positive high-side FET.                                                   |  |

| OUTP     | 23,25           | H-bridge positive output.                                                               |  |

| SDZ         | 29 | Shutdown pin (low = enter shutdown, high = exit shutdown). TTL logic levels with compliance to AVDD.            |

|-------------|----|-----------------------------------------------------------------------------------------------------------------|

| FAULTZ      | 30 | Open drain output used to display general fault, including SCP, OTP, DCP fault status (low=fault, high=normal). |

| INP         | 31 | Positive audio input. Biased at 1.7V.                                                                           |

| INN         | 32 | Negative audio input. Biased at 1.7V                                                                            |

| Thermal Pad | 33 | Connect to GND for best system performance.                                                                     |

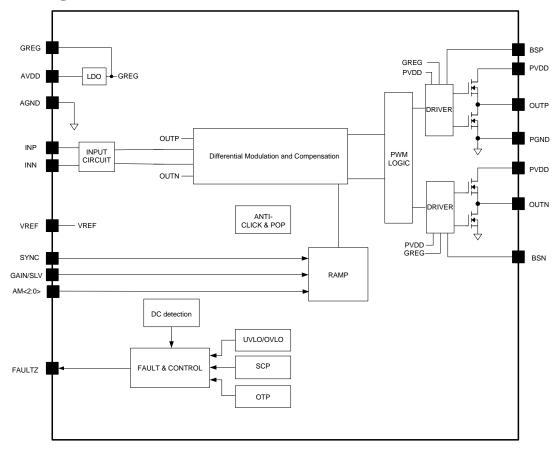

## **Block Diagram**

Figure 2. Block Diagram

# Absolute Maximum Ratings (Note 1)

| 8 , , ,                                      |                                     |

|----------------------------------------------|-------------------------------------|

| AVDD, PVDD                                   |                                     |

| INP, INN                                     |                                     |

| MODSEL, SDZ, MUTE, AM2, AM1, AM0             |                                     |

| VREF, GAIN/SLV, SYNC                         |                                     |

| Minimum Load Resistance Output Configuration | 2.5Ω                                |

| Junction Temperature (T <sub>J</sub> )       | $-40^{\circ}$ C to $+150^{\circ}$ C |

| Storage Temperature                          | 40°C to +125°C                      |

| Package Thermal Resistance (Note 2)          |                                     |

| heta JA                                      | 22°C/W                              |

| $\theta$ JC                                  | 8°C/W                               |

| <b>Recommended Operating Conditions</b>      |                                     |

| Supply Voltage Range                         | 5.6V to 26V                         |

| Junction Temperature Range                   |                                     |

## **Electrical Characteristics**

$(T_A = 25^{\circ}C, V_{DD}=18V, R_L=4\Omega, Gain=26dB, unless otherwise specified)$

| $T_A = 25^{\circ}\text{C}, V_{DD}=18\text{V}, R_L=4\Omega, Gain=26dB, unless otherwise specified}$<br>Parameter Symbol Test Conditions Min Typ Max |                     |                                                         |          | Unit |      |          |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------|----------|------|------|----------|--|

| DC Characteristics                                                                                                                                 |                     |                                                         |          |      |      |          |  |

| AVDD, PVDD                                                                                                                                         | $V_{DD}$            |                                                         | 5.6      |      | 26   | V        |  |

|                                                                                                                                                    |                     | SDZ=high, no load or filter (Note 4)                    |          | 28.5 |      |          |  |

| Quiescent Supply Current                                                                                                                           | $I_Q$               | SDZ=high, with snubber and                              |          | 37.7 |      | mA       |  |

| Quiescent Supply Current                                                                                                                           | IQ                  | LC:10µH+680nF(Note 4)                                   |          | 31.1 |      |          |  |

|                                                                                                                                                    |                     | SDZ=Low, no load                                        |          | 100  | 122  | μΑ       |  |

|                                                                                                                                                    |                     | SDZ, SYNC, MUTE, AM2, AM1,                              | 2.05     |      |      |          |  |

| High-level Input Voltage                                                                                                                           | $V_{IH}$            | AM0                                                     | 2.05     |      |      | V        |  |

|                                                                                                                                                    |                     | MODSEL (Note 4)                                         |          | 1.75 |      |          |  |

|                                                                                                                                                    |                     | SDZ, SYNC, MUTE, AM2, AM1,                              |          |      | 0.75 |          |  |

| Low-level Input Voltage                                                                                                                            | VIL                 | AM0                                                     |          |      | 0.75 | V        |  |

|                                                                                                                                                    |                     | MODSEL (Note 4)                                         |          | 1    |      |          |  |

| T 1 10                                                                                                                                             |                     | FAULTZ, RPULL-UP=100k,                                  |          | 0.00 |      | **       |  |

| Low-level Output Voltage                                                                                                                           | V <sub>OL</sub>     | PVDD=26V                                                |          | 0.22 |      | V        |  |

|                                                                                                                                                    |                     | MODESEL, MUTE, AM2, AM1,                                | 0.4      |      | 0.4  |          |  |

| High-level Input Current                                                                                                                           | I <sub>IH</sub>     | AM0, $V_I = 2V$                                         | -0.1     |      | 0.1  | μA       |  |

| S                                                                                                                                                  |                     | SDZ, V <sub>I</sub> = 2V                                | 4        | 6    | 8    | 1 '      |  |

| Drain-Source On-State Resistance                                                                                                                   | R <sub>DS(ON)</sub> | 552, 11 2 1                                             |          | 60   |      | mΩ       |  |

|                                                                                                                                                    | 22(31)              | R1=Open, R2=5.6kΩ, no load                              |          |      |      |          |  |

|                                                                                                                                                    |                     | (Note 4)                                                |          | 20   |      | dB       |  |

| Gain(Master)                                                                                                                                       |                     | R1=100kΩ, R2=20kΩ, no load                              | 25.5     | 26   | 26.5 |          |  |

|                                                                                                                                                    | G                   | R1=100kΩ, R2=39kΩ, no load                              | oad      | 32   |      |          |  |

|                                                                                                                                                    |                     | (Note 4)                                                |          | 32   |      |          |  |

|                                                                                                                                                    |                     | R1=75k $\Omega$ , R2=47k $\Omega$ , no load             |          | 36   |      |          |  |

|                                                                                                                                                    |                     | (Note 4)                                                |          |      |      |          |  |

|                                                                                                                                                    |                     | R1=51k $\Omega$ , R2=51k $\Omega$ , no load<br>(Note 4) |          | 20   |      |          |  |

|                                                                                                                                                    |                     | $R1=47k\Omega$ , $R2=75k\Omega$ , no load               |          |      |      | dB       |  |

| Gain(Slave)                                                                                                                                        | G                   | (Note 4)                                                |          | 26   |      |          |  |

| (4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4                                                                                                             |                     | R1=39kΩ, R2=100kΩ, no load                              |          | 22   |      |          |  |

|                                                                                                                                                    |                     | (Note 4)                                                |          | 32   |      |          |  |

|                                                                                                                                                    |                     | R1=16kΩ, R2=100kΩ, no load                              | 35.5     | 36   | 36.5 |          |  |

| Turn-on Time(Note 4)                                                                                                                               | ton                 | SDZ=High                                                |          | 45   |      | ms       |  |

| Turn-off Time(Note 4)                                                                                                                              | toff                | SDZ=Low                                                 |          | 1    |      | μs       |  |

| Output Offset Voltage                                                                                                                              | Vos                 | V <sub>IN</sub> =0Vrms, Measured Differentially         |          | 1.5  | 15   | mV       |  |

|                                                                                                                                                    |                     | at $V_{DD} = 18V$                                       |          |      |      |          |  |

| Gate Drive Supply                                                                                                                                  | GREG                | SDZ=2V, V <sub>IN</sub> =0Vrms                          | 3.2      | 3.4  | 3.6  | V        |  |

|                                                                                                                                                    |                     | AM2=0,AM1=0,AM0=0                                       | 350      | 400  | 428  |          |  |

|                                                                                                                                                    |                     | AM2=0,AM1=0,AM0=1                                       | 437.5    | 500  | 535  |          |  |

|                                                                                                                                                    |                     | AM2=0,AM1=1,AM0=0                                       | 525      | 600  | 642  |          |  |

| PWM Frequency                                                                                                                                      | f <sub>PWM</sub>    | AM2=0,AM1=1,AM0=1                                       | 875      | 1000 | 1070 | kHz      |  |

| 1 will requency                                                                                                                                    | 11 WW               | AM2=1,AM1=0,AM0=0                                       | 1050     | 1200 | 1284 | KIIZ     |  |

|                                                                                                                                                    |                     | AM2=1,AM1=0,AM0=1                                       | Reserved |      |      |          |  |

|                                                                                                                                                    |                     | AM2=1,AM1=1,AM0=0                                       | Reserved |      |      |          |  |

|                                                                                                                                                    |                     | AM2=1,AM1=1,AM0=1                                       | Reserved |      |      |          |  |

| AC Characteristics(Note 4)                                                                                                                         | <u> </u>            |                                                         | <u> </u> |      | ı    | ı        |  |

| Output Integrated Noise                                                                                                                            | Vn                  | 20Hz to 22kHz, A-weighted filter,                       |          | 65   |      | μV       |  |

|                                                                                                                                                    |                     | Gain=20dB  Max output at THD+N<1%,                      |          |      |      | <u>'</u> |  |

| Signal to Noise Ratio                                                                                                                              | SNR                 | V <sub>DD</sub> =6V, f=1kHz, Gain=20dB, A-              |          | 96   |      | dB       |  |

| Signal to 140ise Ratio                                                                                                                             |                     | weighted                                                |          | 70   |      | uБ       |  |

|                                                    |                        | Max output at THD+N<1%,<br>V <sub>DD</sub> =12V, f=1kHz, Gain=20dB, A-weighted           |      | 102   |      |    |  |

|----------------------------------------------------|------------------------|------------------------------------------------------------------------------------------|------|-------|------|----|--|

|                                                    |                        | Max output at THD+N<1%,<br>V <sub>DD</sub> =18V, f=1kHz, Gain=20dB, A-<br>weighted       |      | 106   |      |    |  |

|                                                    |                        | Max output at THD+N<1%,<br>V <sub>DD</sub> =24V, f=1kHz, Gain=20dB, A-weighted           |      | 108   |      |    |  |

|                                                    |                        | Max output at THD+N<1%,<br>VDD=18V, f=1kHz, Gain=20dB,<br>A-weighted, R <sub>L</sub> =8Ω |      | 106   |      |    |  |

|                                                    |                        | V <sub>DD</sub> =6V, f=1kHz, Po=1W                                                       |      | 0.04  |      |    |  |

|                                                    |                        | V <sub>DD</sub> =12V, f=1kHz, Po=1W                                                      |      | 0.033 |      |    |  |

|                                                    |                        | V <sub>DD</sub> =12V, f=1kHz, Po=7.8W                                                    |      | 0.07  |      |    |  |

|                                                    |                        | V <sub>DD</sub> =18V, f=1kHz, Po=1W                                                      |      | 0.028 |      |    |  |

|                                                    |                        | V <sub>DD</sub> =18V, f=1kHz, Po=17W                                                     |      | 0.279 |      | %  |  |

| Total Harmonic Distortion + Noise                  | THD+N                  | V <sub>DD</sub> =24V, f=1kHz, Po=1W                                                      |      | 0.025 |      |    |  |

|                                                    |                        | V <sub>DD</sub> =24V, f=1kHz, Po=30W                                                     |      | 0.456 |      |    |  |

|                                                    |                        | $V_{DD}$ =18V, f=1kHz, $R_L$ =8 $\Omega$ , $P_0$ =1W                                     |      | 0.012 |      |    |  |

|                                                    |                        | $V_{DD}$ =18V, f=1kHz, $R_L$ =8 $\Omega$ , $P_0$ =9.5W                                   |      | 0.059 |      |    |  |

|                                                    |                        | V <sub>DD</sub> =6V, f=1kHz, 1% THD+N                                                    |      | 3.9   |      |    |  |

|                                                    |                        | V <sub>DD</sub> =6V, f=1kHz, 10% THD+N                                                   |      | 4.9   |      |    |  |

|                                                    |                        | V <sub>DD</sub> =12V, f=1kHz, 1% THD+N                                                   |      | 15.6  |      |    |  |

|                                                    |                        | V <sub>DD</sub> =12V, f=1kHz, 10% THD+N                                                  |      | 19.7  |      |    |  |

|                                                    |                        | V <sub>DD</sub> =18V, f=1kHz, 1% THD+N                                                   |      | 35    |      | 1  |  |

| Output Power                                       | Po                     | V <sub>DD</sub> =18V, f=1kHz, 10% THD+N                                                  |      | 43.7  |      | W  |  |

|                                                    |                        | V <sub>DD</sub> =24V, f=1kHz, 1% THD+N                                                   |      | 61    |      |    |  |

|                                                    |                        | $V_{DD}=18V$ , $R_L=8\Omega$ , $f=1kHz$ , 1% THD+N                                       |      | 19.3  |      |    |  |

|                                                    |                        | $V_{DD}$ =18V, $R_L$ =8 $\Omega$ , $f$ =1 $k$ Hz, 10% THD+N                              |      | 24    |      |    |  |

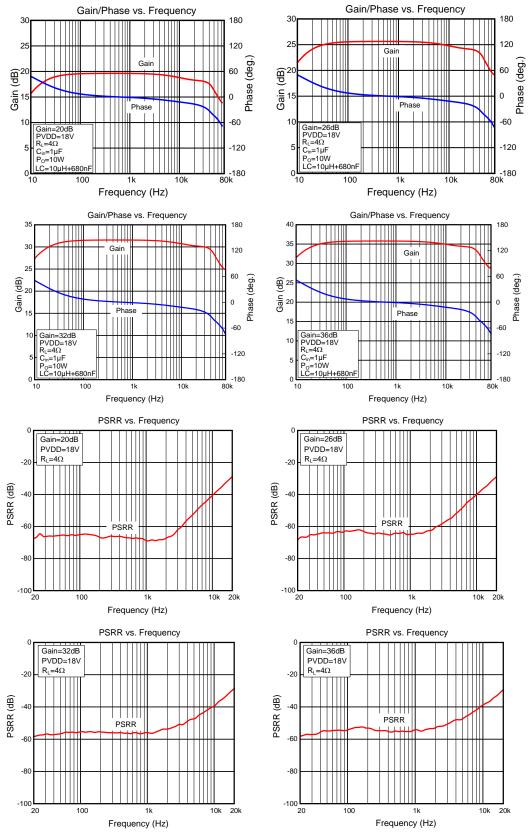

| Power Supply Rejection Ratio                       | PSRR                   | 200mV <sub>PP</sub> ripple, f=1kHz,<br>Gain=20dB                                         |      | -64.5 |      | dB |  |

| Protection                                         |                        |                                                                                          |      |       | ·    |    |  |

| V <sub>DD</sub> Under Voltage Lockout              | V <sub>UVLO_RISE</sub> | V <sub>DD</sub> Rising                                                                   |      | 5.5   | 5.6  | V  |  |

| Voltage                                            | Vuvlo_fall             | V <sub>DD</sub> Falling                                                                  | 4.9  | 5.2   | 5.3  | V  |  |

| V <sub>DD</sub> Over Voltage Lockout Voltage       | Vovlo_rise             | V <sub>DD</sub> Rising                                                                   | 21.7 | 31    | 32.5 | V  |  |

|                                                    | V <sub>OVLO_FALL</sub> | V <sub>DD</sub> Falling                                                                  | 26.5 | 28    |      | V  |  |

| Short Circuit Protection Current<br>Limit (Note 4) | Isc                    |                                                                                          |      | 28    |      | Α  |  |

| Thermal Shutdown Temperature (Note 4)              | T <sub>SD</sub>        |                                                                                          |      | 150   |      | °C |  |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2**: DC voltage rating could be derated a little according to the possible switching spike on switching node if the snubber is not appropriate enough.

Note 3:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25$ °C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note 4: Typical test value on demonstration board, guarantee by design.

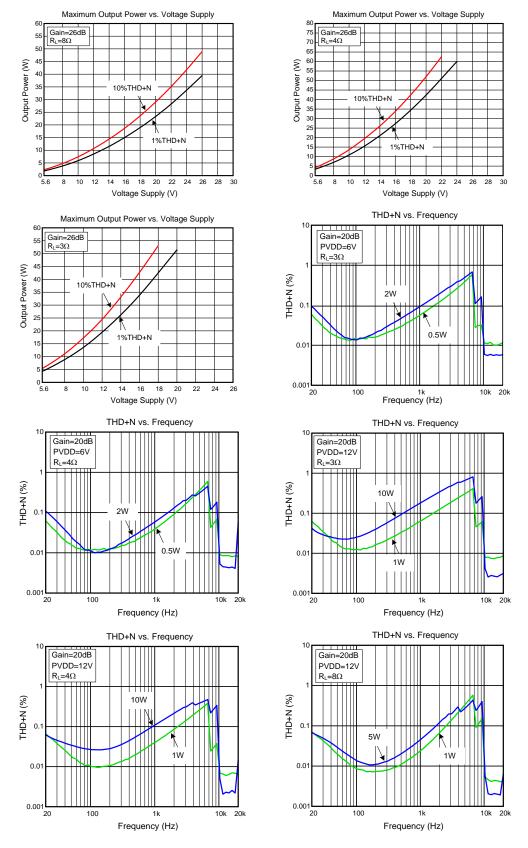

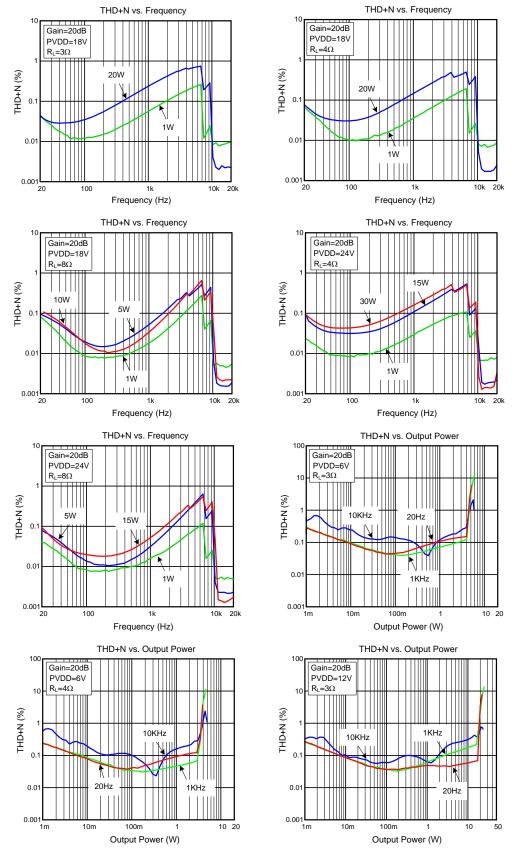

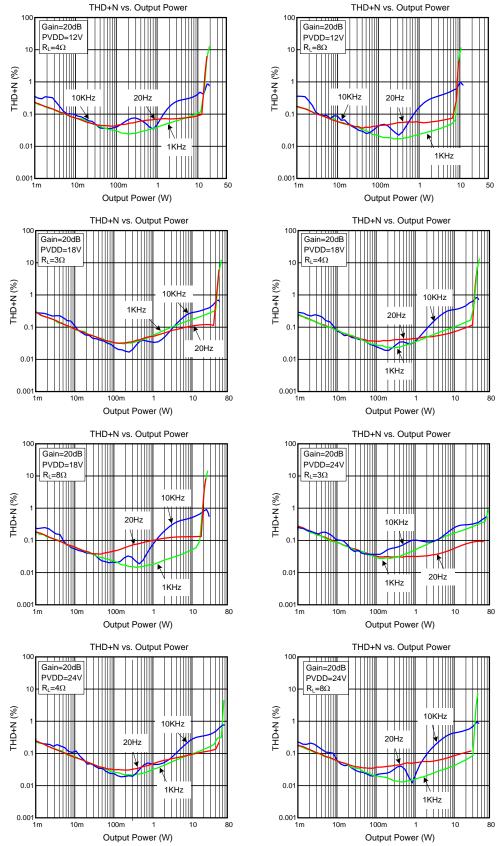

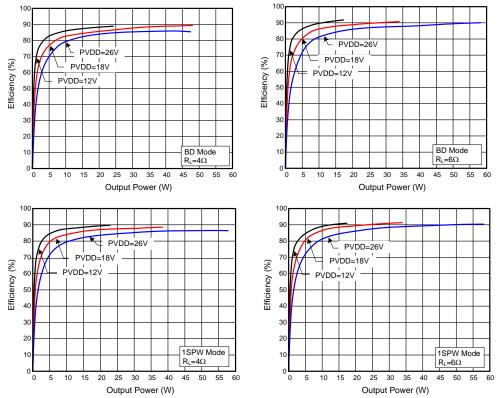

# **Typical Performance Characteristics**

### **Function Description**

This section focuses on the description of SY6018B Class-D function block operation.

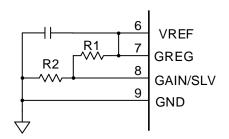

#### Gain & Master/Slave Mode Setting

The gain and master/slave mode of the SY6018B is set by the GAIN/SLV pin. An internal sampling circuit is used for detecting the 8 status. The first four stages set the GAIN in Master Mode in gains of 20,26,32,36dB respectively, while the other four stages set the GAIN in Slave Mode in gains of 20,26,32,36dB respectively. Table 1 lists the recommended resistors and states as well as gain. Figure 3 is the typical circuit for GAIN/SLV pin. The resistor tolerance should be 5% or better.

In Master mode, SYNC terminal is an output while in Slave mode, SYNC is an input for a clock input. TTL logic levels compliance to GREG.

| MODE   | GAIN(dB) | R1 (to GREG, $k\Omega$ ) | R2 (to GND, $k\Omega$ ) |

|--------|----------|--------------------------|-------------------------|

| Master | 20       | OPEN                     | 5.6                     |

| Master | 26       | 100                      | 20                      |

| Master | 32       | 100                      | 39                      |

| Master | 36       | 75                       | 47                      |

| Slave  | 20       | 51                       | 51                      |

| Slave  | 26       | 47                       | 75                      |

| Slave  | 32       | 39                       | 100                     |

| Slave  | 36       | 16                       | 100                     |

Table1. Gain and Master/Slave Setting

Figure 3. Gain and Master/Slave setting circuit

#### **Modulation Scheme**

The SY6018B has two modulation schemes: BD modulation and 1SPW modulation, which is set via the MODSEL pin.

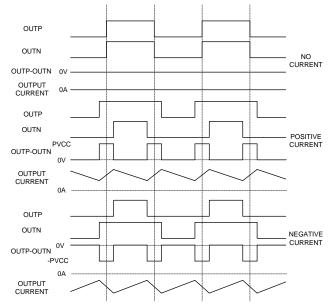

#### MODSEL=LOW: BD-Modulation

The SY6018B uses BD mode modulation scheme as Figure 4. Each output is switching from 0V to the supply voltage. The OUTP and OUTN are in phase with each other with no input so that there is little or no current in the speaker. The duty cycle of OUTP is greater than 50% and OUTN is less than 50% for positive output voltages. The duty cycle of OUTP is less than 50% and OUTN is greater than 50% for negative output voltages. The voltage across the load sits at 0V throughout most of the switching period, greatly reducing the switching current, which will reduce any I<sup>2</sup>R losses in the load.

Figure 4. BD-Modulation

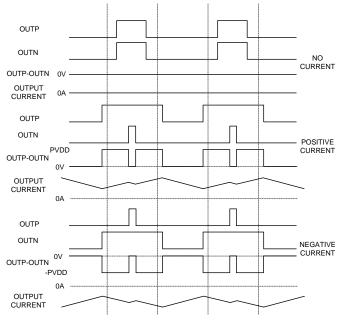

#### MODSEL=HIGH: 1SPW-Modulation

The 1SPW mode is different from traditional modulation scheme in order to achieve higher efficiency with a slight penalty in THD degradation and more required in the output filter. In 1SPW mode the output operates at 35% modulation during idle conditions. When an audio signal is applied one output will decrease and one will increase.

Figure 5. 1SPW-Modulation

#### Input Capacitor, CI

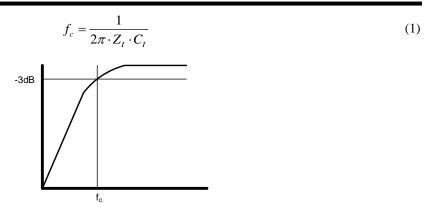

In the typical application, input capacitor  $C_I$  is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case  $C_I$  and the input impedance of the amplifier  $(Z_I)$  form a high-pass filter with the corner frequency determined in Equation 1.

Figure 6. -3dB frequency of HPF

The value of  $C_1$  is important, as it directly affects the bass (low-frequency) performance of the circuit. The input resistance of the SY6018B value is fixed at  $15k\Omega \pm 20\%$ , consider the specification calls for a flat bass response down to 20Hz. Equation 1 is reconfigured as Equation 2.

$$C_I = \frac{1}{2\pi \cdot Z_I \cdot f_c} \tag{2}$$

In this example,  $C_I$  is  $0.53\mu F$ ; so, one would likely choose a value of  $1\mu F$  as this value is commonly used. A further consideration for this capacitor is the leakage path from the input source through the input network,  $C_I$ , and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high-gain applications. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at 1.7V, which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application. Additionally, lead-free solder can create dc offset voltages, and it is important to ensure that boards are cleaned properly.

#### **Differential Inputs**

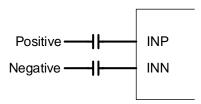

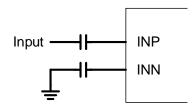

The differential input stage of the amplifier cancels any noise that appears on both input lines of the channel. To use the SY6018B with a differential source, connect the positive lead of the audio source to the INP input and the negative lead from the audio source to the INN input. To use the SY6018B with a single-ended source, ac ground the INP or INN input through a capacitor equal in value to the input capacitor on INN or INP and apply the audio source to either input. In a single-ended input application, the unused input should be ac grounded at the audio source instead of at the device input for best noise performance. For good transient performance, the impedance seen at each of the two differential inputs should be the same. The input signal connection is shown as Figure 7.

The impedance seen at the inputs should be limited to an RC time constant to allow the input dc blocking capacitors to become completely charged during the 45ms power-up time. If the input capacitors are not allowed to completely charge, there will be some additional sensitivity to component matching which can result in pop if the input components are not well matched.

#### (a) Differential Input

(b) Single-ended Input

Figure 7. Input Signal Connection

#### **BSN** and **BSP**

The half H-bridge output stages use only NMOS transistors. Therefore, they require bootstrap capacitors for the high side of each output to turn on correctly. A 220nF ceramic capacitor, rated for at least 25V, must be connected from each output to its corresponding bootstrap input. Specifically, one 220nF capacitor must be connected from OUTP to BSP, and one 220nF capacitor must be connected from OUTN to BSN.

The bootstrap capacitors connected between the BSx pins and their corresponding outputs function as a floating power supply for the high-side N-channel power MOSFET gate-drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.

#### **SDZ Operation**

The SY6018B employs a shutdown mode of operation designed to reduce supply current to the absolute minimum level during periods of nonuse for power conservation. The SDZ input terminal should be held high (see specification table for trip point) during normal operation when the amplifier is in use. Pulling SDZ low causes the outputs to Hi-Z and the amplifier to enter a low-current state. Never leave SDZ unconnected, because amplifier operation would be unpredictable.

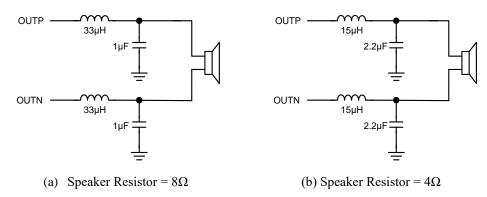

#### Efficiency: LC Filter Required with the Traditional Class-D Modulation Scheme

The main reason that the traditional Class-D amplifier needs an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme, because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is  $2 \times V_{DD}$ , and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The SY6018B modulation scheme has little loss in the load without a filter because the pulses are short and the change in voltage is  $V_{DD}$  instead of  $2 \times V_{DD}$ . As the output power increases, the pulses widen, making the ripple current larger.

Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not needed.

An LC filter with a cutoff frequency less than the Class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance but higher impedance at the switching frequency than the speaker, which results in less power dissipation, therefore increasing efficiency. Figure 8 is the typical LC filter structure.

Figure 8. Typical LC Output Filter, Cutoff Frequency is 27 kHz

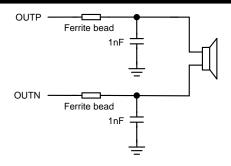

#### **Ferrite Bead Filter Considerations**

When SY6018B is used in low output power application it is possible to design a high efficiency Class-D audio amplifier while minimizing interference to surrounding circuits. It is also possible to accomplish this with only a low-cost ferrite bead filter. In this case it is necessary to carefully select the ferrite bead used in the filter.

One important aspect of the ferrite bead selection is the type of material used in the ferrite bead. Not all ferrite material is alike, so it is important to select a material that is effective in the 10MHz to 100 MHz range which is the key to the operation of the Class-D amplifier. Many of the specifications regulating consumer electronics have emissions limits as low as 30MHz. It is important to use the ferrite bead filter to block radiation in the 30 MHz and above range from appearing on the speaker wires and the power supply lines which are good antennas for these signals. The impedance of the ferrite bead can be used along with a small capacitor with a value in the range of 1nF to reduce the frequency spectrum of the signal to an acceptable level. For best performance, the resonant frequency of the ferrite bead/capacitor filter should be less than 10MHz.

Also, it is important that the ferrite bead is large enough to maintain its impedance at the peak currents expected for the amplifier. Some ferrite bead manufacturers specify the bead impedance at a variety of current levels. In this case it is possible to make sure the ferrite bead maintains an adequate amount of impedance at the peak current the amplifier will see. If these specifications are not available, it is also possible to estimate the bead current handling capability by measuring the resonant frequency of the filter output at very low power and at maximum power. A change of resonant frequency of less than fifty percent under this condition is desirable.

A high quality ceramic capacitor is also needed for the ferrite bead filter. A low ESR capacitor with good temperature and voltage characteristics will work best.

Additional EMC improvements may be obtained by adding snubber networks from each of the Class-D outputs to ground. Suggested values for a simple RC series snubber network would be  $10\Omega$  in series with a 470pF capacitor although design of the snubber network is specific to every application and must be designed taking into account the parasitic reactance of the printed circuit board as well as the audio amp. Take care to evaluate the stress on the component in the snubber network especially if the amp is running at high PVDD. Also, make sure the layout of the snubber network is tight and returns directly to the PGND. The typical ferrite bead filter is shown as Figure 9.

Figure 9. Typical Ferrite Bead EMI Filter

#### When to Use an Output Filter for EMI Suppression

There may be a few circuit instances where it is necessary to add a complete LC reconstruction filter. These circumstances might occur if there are nearby circuits which are very sensitive to noise. In these cases, a classic second order Butterworth filter similar to those shown in the figures below can be used.

Some systems have little power supply decoupling from the AC line but are also subject to line conducted interference (LCI) regulations. These include systems powered by "wall warts" and "power bricks." In these cases, it LC reconstruction filters can be the lowest cost means to pass LCI tests. Common mode chokes using low frequency ferrite material can also be effective at preventing line conducted interference.

#### **AM Avoidance EMI Reduction**

To reduce interference in the AM radio band, the SY6018B has the ability to change the switching frequency via AM<2:0> pins. The recommended frequencies are listed in Table 2. The fundamental frequency and its second harmonic straddle the AM radio band listed. This eliminates the tones that can be present due to the switching frequency being demodulated by the AM radio.

| US<br>AM Frequency(kHz) | European<br>AM Frequency(kHz) | Switching<br>Frequency(kHz)                                      | AM2 | AM1 | AM0 |

|-------------------------|-------------------------------|------------------------------------------------------------------|-----|-----|-----|

|                         | 522-540                       | 400                                                              | 0   | 0   | 0   |

| 540-917                 | 540-914                       | 500                                                              | 0   | 0   | 1   |

| 017 1125                | 014 1122                      | C00/400                                                          | 0   | 1   | 0   |

| 917-1125                | 914-1122                      | $ \begin{array}{c c} 600/400 & 0 \\ \hline 500 & 0 \end{array} $ | 0   | 0   |     |

| 1125-1375               | 1122-1373                     | 500                                                              | 0   | 0   | 1   |

| 1275 1547               | 1272 1540                     | 600/400                                                          | 0   | 1   | 0   |

| 1375-1547               | 1373-1548                     | 600/400                                                          | 0   | 0   | 0   |

| 1547 1700               | 1540 1701                     | C00/500                                                          | 0   | 1   | 0   |

| 1547-1700               | 1548-1701                     | 600/500                                                          | 0   | 0   | 1   |

Table2. AM Frequencies Setting

#### **Protection Circuits**

The device is fully protected against short circuit, over temperature, DC error, over voltage and under voltage. The FAULTZ pin will signal if an error is detected according Table 3.

#### Table3. Fault Reporting

| Fault                     | Triggering Condition                 | Faultz<br>State | Action                | Latched/<br>Self-Clearing |

|---------------------------|--------------------------------------|-----------------|-----------------------|---------------------------|

| Short Circuit             | Output short or short to PVDD or GND | Low             | Output high impedance | Latched                   |

| Over<br>Temperature       | $T_j > 150^{\circ}\mathrm{C}$        | Low             | Output high impedance | Latched                   |

| Too High DC<br>Offset     | I DU OHIDHI VOHAGE                   |                 | Output high impedance | Latched                   |

| Under Voltage<br>for PVDD | PVDD<5.2V                            | -               | Output high impedance | Self-clearing             |

| Over Voltage for PVDD     | PVDD>31V                             | -               | Output high impedance | Self-clearing             |

#### **Short Circuit Protection (SCP)**

The SY6018B has short circuit protection against load is shorted or exceeded. The short circuit protection fault is reported on the FAULTZ pin as a low state. The amplifier outputs are switched to a Hi-Z state when the short circuit protection latch is engaged. The latch can be cleared by cycling the SDZ pin through the low state.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the short-circuit protection latch.

#### **Over Temperature Protection (OTP)**

Thermal protection on the SY6018B prevents damage to the device when the internal die temperature exceeds  $150^{\circ}$ C. There is a  $\pm 15^{\circ}$ C tolerance on this trip point from device to device. Once the die temperature exceeds the thermal set point, the device enters into the shutdown state and the outputs are disabled. This is a latched fault.

Thermal protection faults are reported on the FAULTZ terminal as a low state.

If automatic recovery from the thermal protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the thermal protection latch.

#### **DC Error Protection (DCP)**

The SY6018B has circuitry which will protect the speakers from DC current which might occur due to defective capacitors on the input or shorts on the printed circuit board at the inputs. A DC detect fault will be reported on the FAULTZ pin as a low state. The DC Detect fault will also cause the amplifier to shut down by changing the state of the outputs to Hi-Z.

If automatic recovery from the short circuit protection latch is desired, connect the FAULTZ pin directly to the SDZ pin. This allows the FAULTZ pin function to automatically drive the SDZ pin low which clears the DC Detect protection latch.

A DC Detect Fault is issued when the output differential duty-cycle of either channel exceeds 20% for more than 840ms at the same polarity. Table 4 below shows some examples of the typical DC Detect Protection threshold for several values of the supply voltage. This feature protects the speaker from large DC currents or AC currents less than 1Hz. To avoid nuisance faults due to the DC detect circuit, hold the SDZ pin low at power up until the signals at the inputs are stable. Also, take care to match the impedance seen at the positive and negative inputs to avoid nuisance DC detect faults.

Table 4.DC Detect Threshold

| PVDD(V) | Output Offset Voltage |

|---------|-----------------------|

| 12      | 2.6                   |

| 14      | 3.0                   |

| 16      | 3.6                   |

| 18      | 3.9                   |

#### Under Voltage Lockout (UVLO) and Over Voltage Lockout (OVLO)

If at any time the voltage on the PVDD pin falls below the under voltage or rises above over voltage lockout threshold voltage, all circuitry in the device is disabled and internal logic is reset. Operation resumes when PVDD rises above the UVLO threshold or falls below OVLO threshold.

#### **Power Supply Recommendations**

The power supply requirements for the SY6018B consist of one higher-voltage supply to power the output stage of the speaker amplifier. Several on-chip regulators are included on the SY6018B to generate the voltages necessary for the internal circuitry of the audio path. It is important to note that the voltage regulators which have been integrated are sized only to provide the current necessary to power the internal circuitry. The external pins are provided only as a connection point for off-chip bypass capacitors to filter the supply. Connecting external circuitry to these regulator outputs may result in reduced performance and damage to the device. The high voltage supply, between 5.6V and 26V, supplies the analog circuitry (AVDD) and the power stage (PVDD). The AVDD supply feeds internal LDO.

The SY6018B is a high-performance CMOS audio amplifier that requires adequate power-supply decoupling to ensure that the output total harmonic distortion (THD) is as low as possible. Power-supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power-supply leads. For higher-frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically  $0.1\mu F$  to  $1\mu F$ , placed as close as possible to the device  $V_{DD}$  lead works best. For filtering lower frequency noise signals, a larger aluminum electrolytic capacitor of  $220\mu F$  or greater placed near the audio power amplifier is recommended. The  $220\mu F$  capacitor also serves as local storage capacitor for supplying current during large signal transients on the amplifier outputs. Because the bad low temperature characteristic of aluminum electrolytic capacitor, a ceramic capacitor of  $10\mu F$  should be placed with electrolytic capacitor. The PVDD terminals provide the power to the output transistors, so a  $220\mu F$  or larger capacitor should be placed on each PVDD terminal. A  $10\mu F$  capacitor on the AVDD terminal is adequate. These capacitors must be properly checked for voltage and ripple-current rating to ensure reliability.

#### Printed Circuit Board (PCB) Layout

Because the Class-D switching edges are fast, it is necessary to take care when planning the layout of the printed circuit board. The following suggestions will help to meet EMC requirements.

• Decoupling capacitors—The high-frequency decoupling capacitors should be placed as close to the PVDD and AVDD terminals as possible. Large (220μF or greater) bulk power supply decoupling capacitors should be placed near the SY6018B on the PVDD supplies. Local, high-frequency bypass capacitors should be placed as close to the PVDD pins as possible. These caps can be connected to the IC ground pad directly for an excellent ground connection. Consider adding a small, good quality low ESR ceramic capacitor between 220pF and 1000pF and a larger mid-frequency cap of value between 0.1μF and 1μF also of good quality to the PVDD connections at each end of the chip.

- Keep the current loop from each of the outputs through the conductor and the small filter cap and back to PGND as small and tight as possible. The size of this current loop determines its effectiveness as an antenna.

- Grounding—The AVDD decoupling capacitor should be grounded to analog ground (AGND). The PVDD

decoupling capacitors should connect to PGND. Analog ground and power ground should be connected at the

thermal pad, which should be used as a central ground connection or star ground for the SY6018B.

- Output filter—The LC filter should be placed as close to the output terminals as possible for the best EMI performance. The capacitors used in LC filters should be grounded to power ground.

- Thermal pad—The thermal pad must be soldered to the PCB for proper thermal performance and optimal reliability. The dimensions of the thermal pad and thermal land should be as large as possible. Solid vias should be equally spaced underneath the thermal land. The vias should connect to a solid copper plane, either on an internal layer or on the bottom layer of the PCB.

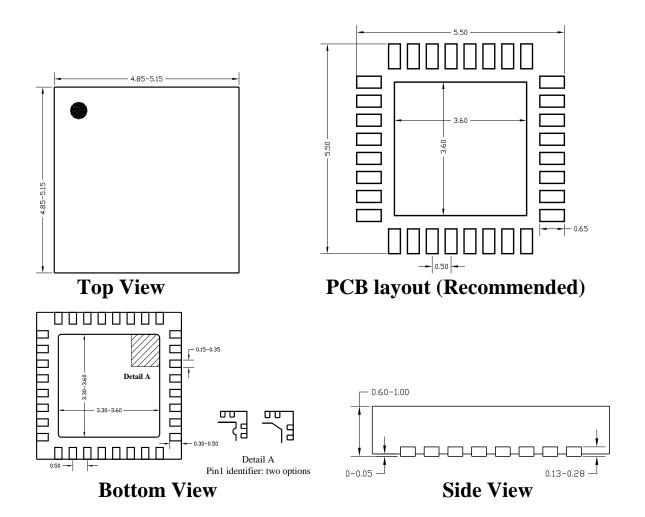

# QFN5×5-32 Package Outline & PCB Layout

Notes: All dimension in millimeter and exclude mold flash & metal burr

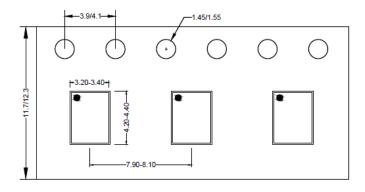

# **Taping & Reel Specification**

## 1. QFN5×5 taping orientation

Feeding direction

## 2. Carrier Tape & Reel specification for packages

| Package<br>types | Tape width (mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|------------------|-----------------|---------------------|---------------------|-----------------------|--------------------|-----------------|

| QFN5x5           | 12              | 8                   | 13"                 | 400                   | 400                | 5000            |

Others: NA.

## **Revision History**

The revision history provided is for informational purpose only and is believed to be accurate, however, not warranted. Please make sure that you have the latest revision.

| Date         | Revision      | Change                                                                                                                                                                                                                                                                               |

|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apr.25, 2022 | Revision 0.9A | <ol> <li>modify the MUTE PIN description as: Mute pin (High=mute, Low=unmute), TTL logic levels with compliance to AVDD.</li> <li>modify the SDZ PIN description as: Shutdown pin (low = enter shutdown, high = exit shutdown). TTL logic levels with compliance to AVDD.</li> </ol> |

| Jan. 5, 2017 | Revision 0.9  | Initial Release                                                                                                                                                                                                                                                                      |

#### IMPORTANT NOTICE

- 1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

- 2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

- 3. **Limited warranty and liability.** Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

- 4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

- 5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

- 6. **No offer to sell or license**. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Silergy under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

© 2022 Silergy Corp.

All Rights Reserved.