# **Application Note: SY6410**

# Cost-save Single Cell Li+ Battery Gauge IC

### **General Description**

The SY6410 is a cost-save gauge IC for single cell lithium-ion (Li+) battery in handheld and portable equipments. The SY6410 senses battery terminal voltage and adopts the proprietary algorithm to calculate the corresponding state of charge (SOC).

Comparing with conventional voltage-based gauge which translates terminal voltage to SOC directly, the sophisticated algorithm in the SY6410 shows great advantage in SOC accuracy. The SY6410 can be classified as advanced voltage-based gauge which does not need current sensors and the SOC accuracy will not diverge with time. SOC and voltage information is accessed by the  $\rm I^2C$  interface. The SY6410 is available in DFN2×2-8.

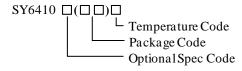

### **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6410DFC       | DFN2×2-8     |      |

#### **Features**

- ±7.5mV/Cell Voltage Measurement

- Provide Accurate State of Charge

- Temperature/Load Variation Compensation

- No Accumulated Errors

- Eliminate Current Sense Resistor

- I<sup>2</sup>C Interface

- Low SOC Alert Indicator

- Compact DFN2×2-8 Package

### **Applications**

- Smart Phones/PDAs

- Portable Game Players

- Digital Still and Video Cameras

- Wireless Handsets

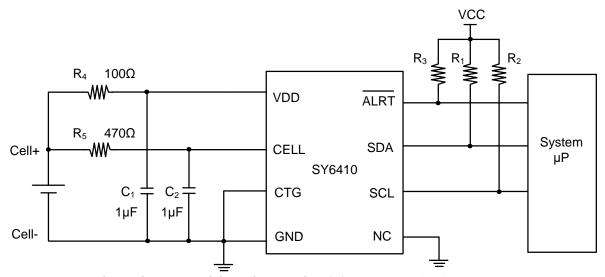

## **Typical Application**

**Note:** CELL pin's resistance  $R_5$  might not be more than 470  $\Omega$ , otherwise it will impact voltage sampling.

Fig.1 Typical Application Circuit

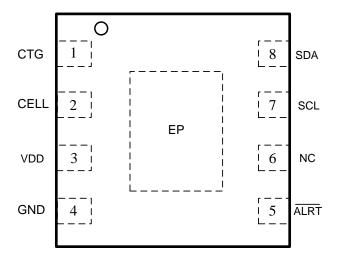

# Pinout (top view)

Top View

(Pad Side Down)

| Part Number | Package type | Top Mark <sup>①</sup> |

|-------------|--------------|-----------------------|

| SY6410DFC   | DFN2×2-8     | Btxyz                 |

Note ①:  $x=year\ code$ ,  $y=week\ code$ ,  $z=lot\ number\ code$ .

| Pin Name | Pin Number | Description                                                                                                                       |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------|

| CTG      | 1          | Connect to GND.                                                                                                                   |

| CELL     | 2          | Battery voltage monitors I/O. Bypass with a $1\mu F$ capacitor to the GND. Connect to battery's positive terminal through $R_5$ . |

| VDD      | 3          | Power supply input. Bypass with a 1μF capacitor to GND. Connect to battery's positive terminal through R <sub>4</sub> .           |

| GND      | 4          | Ground. Connect to battery's negative terminal.                                                                                   |

| ALRT     | 5          | Open-drain output. Low SOC alarm signal. When SOC is below the threshold, this pin will be pulled down.                           |

| NC       | 6          | No connection. NC is recommended to connect to GND.                                                                               |

| SCL      | 7          | I <sup>2</sup> C clock input. SCL has an internal pull-down resistance.                                                           |

| SDA      | 8          | I <sup>2</sup> C data input/output. SDA has an internal pull-down resistance.                                                     |

| EP       |            | Exposed pad. Connected to GND.                                                                                                    |

-20 ℃ to 60 ℃

# Absolute Maximum Ratings (Note 1)

| CELL, VDD, ALRT, SCL, SDA to GND        |                |

|-----------------------------------------|----------------|

| Junction Temperature (T <sub>J</sub> )  | 150 ℃          |

| Storage Temperature                     |                |

| <b>Recommended Operating Conditions</b> |                |

| VDD                                     | 2.7V to 4.5V   |

| CELL                                    | 2.7V to 4.5V   |

| SCL, SDA, ALRT                          |                |

| CTG, NC                                 | Connect to GND |

Operating Temperature Range -----

#### **Electrical Characteristics**

$(2.5V < V_{DD} < 4.5V, T_A = 25 \%$  unless otherwise specified)

| Parameter                              | Symbol                 | <b>Test Conditions</b>                                    | Min                  | Typ | Max | Unit  |

|----------------------------------------|------------------------|-----------------------------------------------------------|----------------------|-----|-----|-------|

| Power Supply                           |                        |                                                           |                      |     |     |       |

| Supply Voltage                         | $V_{DD}$               |                                                           | 2.5                  |     | 4.5 | V     |

| Under Voltage Lockout                  | $V_{\rm UVLO}$         | V <sub>IN</sub> rising                                    |                      |     | 2.5 | V     |

| Threshold                              | V UVLO                 | Hysteresis                                                |                      | 0.3 |     | V     |

| Input Operating Current                | $I_{IN}$               | Active mode                                               |                      | 32  | 40  | μΑ    |

| Input Sleep Mode Current               | I <sub>IN(SLEEP)</sub> | Sleep mode                                                |                      | 0.5 | 2   | μΑ    |

| Time Base Accuracy                     | t <sub>ERR</sub>       | $V_{DD} = 3.6 \text{V}, T_A = 25 ^{\circ}\text{C}$        | -2                   |     | 2   | %     |

| Time Base Accuracy                     | LERK                   | $-20  \text{C} < \text{T}_A < 70  \text{C}(\text{Note3})$ | -4                   |     | 4   | /0    |

| ADC Sample Period                      |                        | Active mode                                               |                      | 250 |     | ms    |

| Voltage Error                          | V <sub>ERR</sub>       | $V_{CELL}$ =3.75V, $T_A$ =25 $^{\circ}$ C                 | -7.5                 |     | 7.5 | mV    |

| voltage Effor                          | V ERR                  | -20 °C <t<sub>A&lt;70 °C(Note3)</t<sub>                   | -30                  |     | 30  | 111 V |

| Voltage Measurement Range              |                        | CELL pin                                                  | 2.5                  |     | 4.5 | V     |

| SDA, SCL Input Logic High              | V <sub>IH</sub>        |                                                           | 1.4                  |     |     | V     |

| SDA, SCL Input Logic Low               | $V_{IL}$               |                                                           |                      |     | 0.5 | V     |

| SDA, ALRT Output Logic Low             | $V_{OL}$               | I <sub>OL</sub> =4mA(Note3)                               |                      |     | 0.4 | V     |

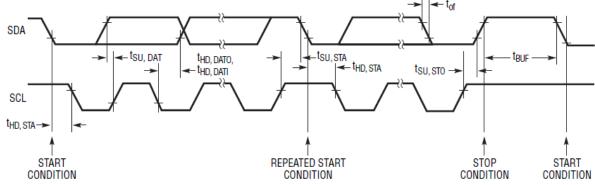

| I <sup>2</sup> C Interface(Note3)      |                        |                                                           |                      |     |     |       |

| SCL Clock Frequency                    | $f_{SCL}$              |                                                           |                      |     | 400 | kHz   |

| Bus Free Time Between<br>Stop/Start    | $t_{ m BUF}$           |                                                           | 1.3                  |     |     | μs    |

| Start Condition(Repeated) Hold<br>Time | t <sub>HD, STA</sub>   |                                                           | 600                  |     |     | ns    |

| Repeat START Set Up Time               | t <sub>SU, STA</sub>   |                                                           | 600                  |     |     | ns    |

| Set Up Time for STOP                   | t <sub>SU, STO</sub>   |                                                           | 600                  |     |     | ns    |

| Data Set Up Time                       | t <sub>SU, DAT</sub>   |                                                           | 100                  |     |     | ns    |

| Data Hold Time                         | thd, dati/o            |                                                           | 0                    |     | 900 | ns    |

| Data Output Fall Time                  | t <sub>Of</sub>        | (Note 2)                                                  | 20+0.1C <sub>B</sub> |     | 300 | ns    |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2:**  $C_B$  is the total capacitance of one bus line in pF ( $C_B \le 400$ pF).

Note 3: Guaranteed by design, not subject to test.

### **Timing Diagram**

Fig.2 I<sup>2</sup>C Timing Diagram

### **Function Description**

As the open circuit voltage (OCV) has a fixed relationship with SOC, SY6410 will calculate OCV to get the SOC. And the calculation of OCV will be based on the present and previous battery terminal voltages. To calculate OCV accurately, the battery parameters should be extracted beforehand. The extracted parameters are written into SY6410 by I<sup>2</sup>C interface. Temperature of the battery pack is measured by the host microcontroller and sent to SY6410 through the I<sup>2</sup>C interface. SY6410 can automatically compensate for battery temperature and load variation. SY6410 will take multi-samples at fixed interval and choose the maximum voltage as the OCV for the initial SOC indication at the battery insertion.

#### **Temperature Compensation**

The battery's performance is influenced by the battery's temperature. SY6410 changes parameters with the measured temperature, which can be written into SY6410 by I<sup>2</sup>C interface in order to maintain SOC accuracy.

#### **Register Details**

All the registers are read or written by I<sup>2</sup>C interface. The address of every register is shown as follow.

| ADDRESS | NAME                  | 16-BIT LSB              |                                                                           |     | DEFAULT |

|---------|-----------------------|-------------------------|---------------------------------------------------------------------------|-----|---------|

| 0x02    | VBAT                  | (2.5/2 <sup>12</sup> )V | ADC sample value of battery.                                              | R   | _       |

| 0x04    | SOC                   | (100/2^16)%             | Battery state of charge.                                                  | R   | _       |

| 0x06    | MODE                  | _                       | Sleep mode enable.                                                        | W   | 0x0000  |

| 0x08    | VERSION               |                         | The IC production version.                                                | R   | _       |

| 0x0C    | CONFIG                |                         | Temperature, sleep mode, alert indicator and configuration.               | R/W | 0x3C1C  |

| 0x18    | VRESET                | _                       | Configure the IC reset threshold value, below which the IC will be reset. | R/W | 0x0333  |

| 0x1A    | The indicator of char |                         | The indicator of charge or discharge.                                     | R   | _       |

| 0xFE    | OXEE POR —            |                         | Make SOC and STATUS registers reset.                                      | R/W | 0xFFFF  |

#### VBAT Register (0x02)

Battery voltage is measured at the CELL pin by an ADC. The battery voltage can be calculated by the following formula:

$Vcell(V) = Reg(VBAT)_{decimal} / 4096 \times 2.5V + 2.5V$

|   |         | MS | B (\ | /BAT)—     | -ADDRES    | SS 0x02   |           |           |           | I         | LSB—A     | DDRES     | S 0x03    |           |           |

|---|---------|----|------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| X | X       | X  | X    | VBAT<br>11 | VBAT<br>10 | VBAT<br>9 | VBAT<br>8 | VBAT<br>7 | VBAT<br>6 | VBAT<br>5 | VBAT<br>4 | VBAT<br>3 | VBAT<br>2 | VBAT<br>1 | VBAT<br>0 |

| M | Msb Lsb |    |      |            |            |           |           | Msb       |           |           |           |           |           |           | Lsb       |

Fig.3 VBAT Register Format

#### SOC Register (0x04)

The SOC register first updates within one second after power starts. The SOC value(%) can be calculated by the following formula:

$SOC(\%) = Reg(SOC)_{decimal} / 65535 \times 100(\%)$

|     | ]                           | MSB (S | SOC)— | ADDRI | ESS 0x0 | )4 |   |  |     |     | LS  | B—AD | DRES | S 0x05 |     |     |

|-----|-----------------------------|--------|-------|-------|---------|----|---|--|-----|-----|-----|------|------|--------|-----|-----|

| SOC | SOC SOC SOC SOC SOC SOC SOC |        |       |       |         |    |   |  |     | SOC | SOC | SOC  | SOC  | SOC    | SOC | SOC |

| 15  | 14                          | 13     | 12    | 11    | 10      | 9  | 8 |  | 7   | 6   | 5   | 4    | 3    | 2      | 1   | 0   |

| Msb | Msb Lsb                     |        |       |       |         |    |   |  | Msb |     |     |      |      |        |     | Lsb |

Fig.4 SOC Register Format

#### MODE Register (0x06)

The system can configure the IC into sleep mode by sending command to MODE Register. The more information about sleep mode is described in **CONFIG Register**.

|     | MSB—ADDRESS 0x06 |              |   |   |   |   |   |  |   |   |   | -ADI | RES | S 02 | k07 |     |

|-----|------------------|--------------|---|---|---|---|---|--|---|---|---|------|-----|------|-----|-----|

| X   | X                | Sleep Enable | X | X | X | X | X |  | X | X | X | X    | X   | X    | X   | X   |

| Msb | Msb Lsb          |              |   |   |   |   |   |  |   |   |   |      |     |      | ]   | Lsb |

Fig.5 MODE Register Format

#### **VERSION Register (0x08)**

This register's value is the version of the IC.

#### **CONFIG Register (0x0C)**

This register contains four parts: TEMP, SLEEP, ALERT and ALTHD.

#### 1. Temperature configuration

TEMP is the value of battery's temperature, which can be written by  $I^2C$  interface. The temperature is used for battery's temperature compensation. In order to get enough accuracy at different temperature, it is necessary for the system to have the function to detect temperature. The default value of TEMP is  $0x3C(20\,C)$ . The following formula shows how to calculate TEMP.

TEMP = INT{temperature ( $^{\circ}$ C)+40}

Note: INT means to translate real number to integer by rejecting the fractional part. The operation temperature range is  $-20^{\circ}$ C to  $60^{\circ}$ C.

#### 2. Sleep mode configuration

SLEEP configures the IC in or out of sleep mode. The SLEEP bit default value is 0.

To enter sleep mode, write Sleep Enable = 1(MODE Register) and SLEEP = 1(CONFIG Register). If write or read anything through  $I^2C$ , it will get out of sleep mode and reset to work again.

#### 3. ALERT configuration

The bit ALERT is the indicator of low SOC. This ALERT's default value is 0. ALTHD sets the SOC threshold. The value is (32-ALTHD)% (e.g. 00000b -> 32%, 11111b -> 1%).

When the SOC is lower than SOC threshold,

- The bit ALERT will be set high by the IC.

- The IC will make the pin ALRT low.

Then, write the bit ALERT= 0 to clear it,

- The bit ALERT will be set low by the IC.

- The pin ALRT will turn high again.

|           |           | MSB       | —ADD      | RESS 0    | x0C       |           |           |  |       | LSB—A | ADDRESS ( | Ox0D              |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|-------|-------|-----------|-------------------|

| TEMP<br>7 | TEMP<br>6 | TEMP<br>5 | TEMP<br>4 | TEMP<br>3 | TEMP<br>2 | TEMP<br>1 | TEMP<br>0 |  | SLEEP | X     | ALERT     | ALTHD4~<br>ALTHD0 |

| Msb       |           |           |           |           | -         | Msb       |           |  | Lsb   |       |           |                   |

Fig.6 CONFIG Register Format

#### VRESET Register (0x18)

This register defines the reset voltage. If the battery voltage ( $V_{CELL}$ ) is lower than  $V_{RESET}$ , then the IC will be reset and the SOC value will be held at 0%. VRESET Register can be set by this formula:

$VRESET_reg = (V_{RESET}(V) - 2.5V)/2.5V \times 4096$

|   | ]             | MS] | B (\ | <b>VRESET</b> | )—ADD | RESS 0x1 | 18          |             |             | L           | SB—AI       | DDRESS      | 0x19     |             |             |

|---|---------------|-----|------|---------------|-------|----------|-------------|-------------|-------------|-------------|-------------|-------------|----------|-------------|-------------|

| X | v   v   v   v |     |      |               |       |          | VRESET<br>8 | VRESET<br>7 | VRESET<br>6 | VRESET<br>5 | VRESET<br>4 | VRESET<br>3 | VRESET 2 | VRESET<br>1 | VRESET<br>0 |

| M | Msb Lsb       |     |      |               |       |          |             | Msb         |             |             |             | •           |          |             | Lsb         |

Fig.7 VRESET Register Format

#### STATUS Register (0x1A)

FLAG is the indicator of charge(FLAG=1) or discharge(FLAG=0).

|                 | MSB ( | STAT | US)— | -ADD | RESS | 0x1A |  |  |     |   | L | SB—AI | DRESS | 0x1B |   |      |

|-----------------|-------|------|------|------|------|------|--|--|-----|---|---|-------|-------|------|---|------|

| x x x x x x x x |       |      |      |      |      |      |  |  | X   | X | X | X     | X     | X    | X | FLAG |

| Msb             |       |      |      |      |      |      |  |  | Msb |   |   |       |       |      |   | Lsb  |

Fig.8 STATUS Register Format

#### POR Register (0xFE)

Writing a value of 0x5400 to this register causes the IC's read only registers (e.g. SOC, STATUS register) to completely reset as if power had been removed. Then write a value of 0xFFFF to this register and the IC will work again.

#### **Battery Parameters**

All the battery parameters are read or written by I<sup>2</sup>C interface and stored in MTP.

When program data into MTP, set VDD =  $4 \sim 5.5$  V.

When SY6410 works normally to measure voltage and SOC, the MCU should not send command to write or read the MTP, otherwise the MCU will read SOC value by mistake. There are two ways to avoid this situation.

- 1. Shut down the power after writing and reading MTP. And then do not read or write the MTP any more when SY6410 is working normally.

- 2. After power on and then check the data in MTP, the IC will enter sleep mode by writing Sleep Enable = 1(MODE Register) and SLEEP =1(CONFIG Register) and then exit sleep mode by writing or reading anything through the I<sup>2</sup>C. Using this method, it can exit the status of MTP's operation and then SY6410 can work normally.

AN\_SY6410 Rev.0.9 Silergy Corp. 6

© 2022 Silergy Corp. All Rights Reserved.

| ADDRESS      | 16-BIT LSB | DESCRIPTION        | READ/WRITE | DEFAULT |

|--------------|------------|--------------------|------------|---------|

| 0x00 to 0x7F | _          | Battery parameters | R/W        | _       |

#### I<sup>2</sup>C Compatible Interface

The I<sup>2</sup>C interface supports clock at speed up to 400kHz and adopts the standard I<sup>2</sup>C commands. The SY6410 always operates as a slave device, receiving and transmitting data under the control of a master device. The master initiates all transactions on the bus and generates the SCL signal, as well as the START and STOP bits, which begin and end each transaction.

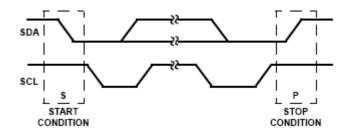

#### **START and STOP Conditions**

The SY6410 is controlled via a compatible I<sup>2</sup>C interface. The START condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The STOP condition is a LOW to HIGH transition on the SDA line while SCL is HIGH. A STOP condition must be sent before the next START condition. The I<sup>2</sup>C master always generates the START and STOP conditions.

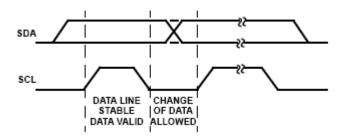

#### **Data Validity**

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW.

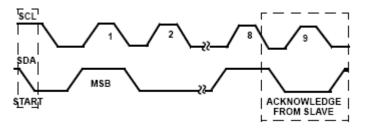

#### **Acknowledge**

Each address and data transmission uses 9-clock pulses. The ninth pulse is the acknowledge bit (ACK). After the START condition, the master sends 7-slave address bits and a  $R/\overline{W}$  bit during the next 8-clock pulses. During the ninth clock pulse, the slave device which recognizes its own address holds the data line low to acknowledge. The acknowledge bit is also used by both the master and the slave to acknowledge receipt of register address and data.

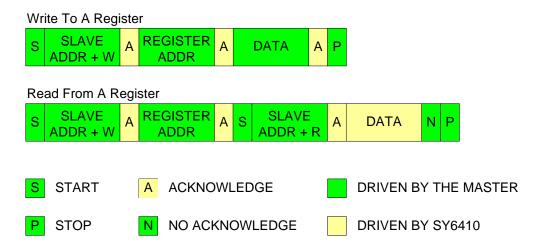

#### **Data Transactions**

All transactions start with a control byte sent from the I<sup>2</sup>C master device. The control byte begins with a START condition, followed by 7-bits of a slave address (0110000 for the SY6410) and the read/write (R/ $\overline{W}$ ) bit. R/ $\overline{W}$  = 0 selects a write transaction with the following bytes being written by the master to the slave. R/ $\overline{W}$  = 1 selects a read transaction with the following bytes being read from the slave by the master. If any slave devices on the I<sup>2</sup>C BUS recognize their address, they will acknowledge by pulling the SDA line low for the last clock cycle in the control byte. If no slaves exist at that address or the slaves are not ready to communicate, the data line will be 1, indicating a Not Acknowledge condition. Once the control byte is sent, and the SY6410 acknowledges it, the 2nd byte sent by the master must be a register address byte. The register address byte tells the SY6410 which register to be written or read by the master. Once the SY6410 receives a register address byte it will respond with an ACKNOWLEDGE.

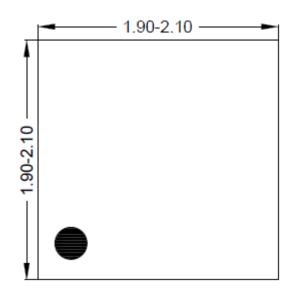

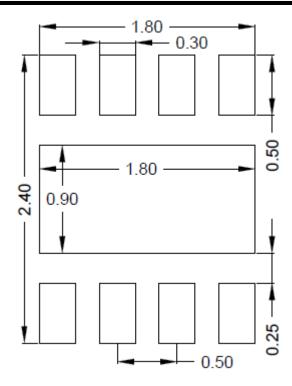

# **DFN2×2-8 Package Outline**

**Top View**

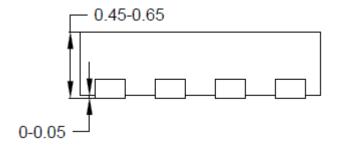

**Side View**

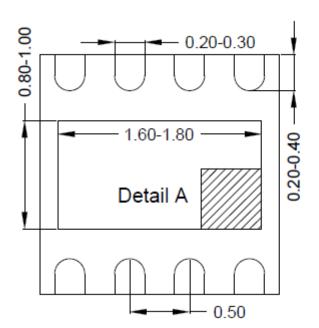

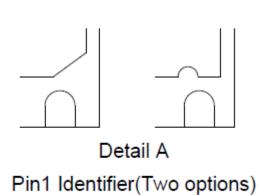

**Bottom View**

Recommended PCB Layout (Reference Only)

Notes: All dimension in millimeter and exclude mold flash & metal burr.

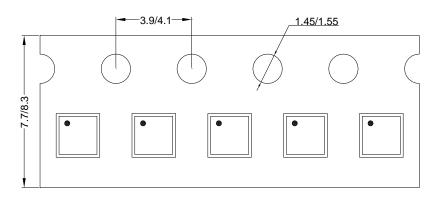

# **Taping & Reel Specification**

# 1. DFN2×2-8 Taping orientation

Feeding direction ——

# 2. Carrier Tape & Reel specification for packages

| Package types | Tape width | Pocket    | Reel size | Trailer *  | Leader *    | Qty per reel |

|---------------|------------|-----------|-----------|------------|-------------|--------------|

|               | (mm)       | pitch(mm) | (Inch)    | length(mm) | length (mm) | (pcs)        |

| DFN2×2        | 8          | 4         | 7''       | 400        | 160         | 3000         |

### 3. Others: NA

#### IMPORTANT NOTICE

- 1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

- 2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

- 3. **Limited warranty and liability.** Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

- 4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

- 5. **Terms and conditions of commercial sale.** Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

- 6. No offer to sell or license. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Silergy under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

© 2022 Silergy Corp.

All Rights Reserved.