Datasheet Version: 1E http://wch.cn

# 1. Overview

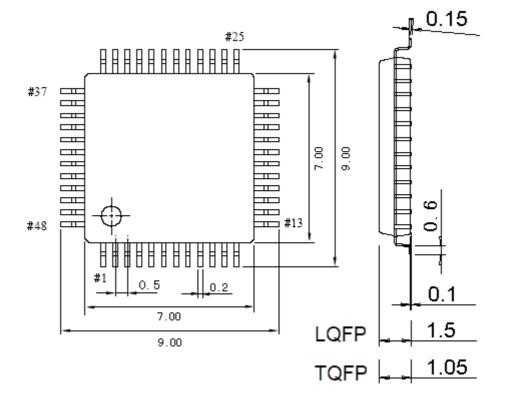

The CH547 is an enhanced E8051 MCU compatible with MCS51 instruction set. 79% of its instructions are single-byte single-cycle instructions, and the average instruction speed is 8 to 15 times faster than that of the standard MCS51.

The CH547 supports up to 48MHz system clock, built-in 64KB Flash-ROM, 256B on-chip iRAM, 2KB on-chip xRAM, and xRAM supports DMA mode.

The CH547 has a built-in 12-bit ADC converter, capacitive touch key detection module, temperature sensor (TS), built-in clock, 3 timers and 1-channel signal capture, 4 channels of PWM, 4 UARTs, SPI and other functional modules. It supports full speed and low speed USB-Device modes.

The CH546 is a simplified version of CH547, with 32KB Flash-ROM, UART0 only, 8 channels of ADC and touch key detection, 2 channels pf PWM. Others of CH546 are the same as that of CH547, please directly refer to CH547 datasheet and technical resources.

| Product<br>No. | Flash-ROM<br>Boot ROM | xRAM<br>iRAM |     | USB<br>device | TS      | Timer | Signal capture | 8-bit<br>PWM | UART | SPI master<br>SPI slave | 12-bit<br>ADC  | Capacitive<br>Touch key |

|----------------|-----------------------|--------------|-----|---------------|---------|-------|----------------|--------------|------|-------------------------|----------------|-------------------------|

| CH547          | 60KB+3KB              | 1024         | 1KB | Full/low      | Support | 3     | 1 channel      | 4 channels   | 4    | 2 in 1                  | 12<br>channels | 12<br>channels          |

| CH546          | 32KB+3KB              | +256         | IKD | speed         | Support | 5     | 1 chamier      | 2 channels   | 1    | 2 111 1                 | 8 channels     | 8 channels              |

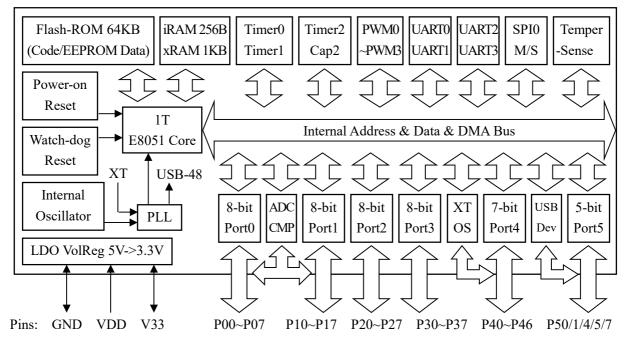

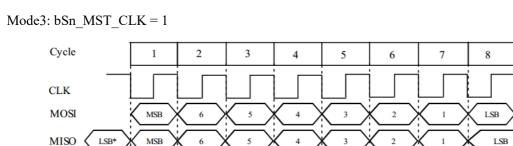

Here is CH547 internal block diagram, for reference only.

# 2. Features

- Core: Enhanced E8051 core, compatible with MCS51 instruction set, 79% of its instructions are single-byte single-cycle instructions, and the average instruction speed is 8 to 15 times faster than that of the standard MCS51, with special XRAM data fast copy instruction, and dual DPTR pointer.

- ROM: Non-volatile 64KB Flash-ROM, which supports 10K writing cycles, it can be all used for program memory. Or it can be divided into 3 pieces, 60KB for program memory, 1KB for data-flash EEPROM and 3KB for BootLoader/ISP code.

- EEPROM: 1KB data memory EEPROM, it is divided into 16 independent blocks, and supports byte read, byte write, block write (1 to 64 bytes), and block erase (64 bytes). It generally supports 100K (not guaranteed) writing cycles in a typical environment.

- OTP: 32B One time Programmable data memory (OTP). It supports dual word (4 bytes) read, single byte write.

- RAM: 256B on-chip iRAM, for fast data cache and stack pointer. 1KB on-chip xRAM, for mass data or DMA operation.

- USB: Built-in USB device controller and USB transceiver, supports USB 2.0 full speed (12Mbps) and low speed (1.5Mbps). Maximum support 64-byte packet, built-in FIFO, and support DMA mode.

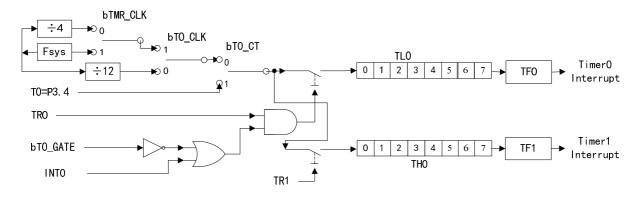

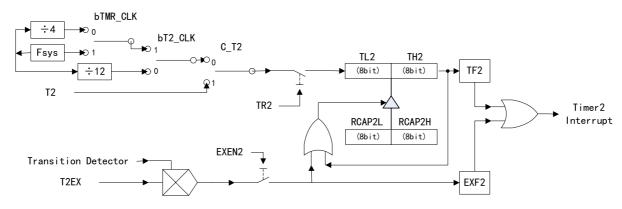

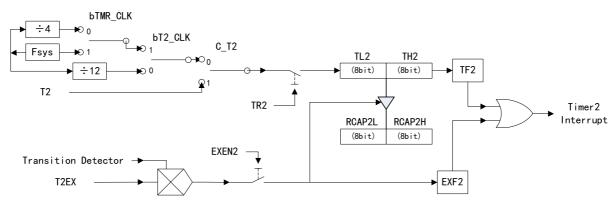

- Timer: 3 timers. T0, T1 and T2 are standard MCS51 timers.

- Capture: T2 supports 1-channel signal capture.

- PWM: 4 PWM outputs, support standard 8-bit data or fast 6-bit data.

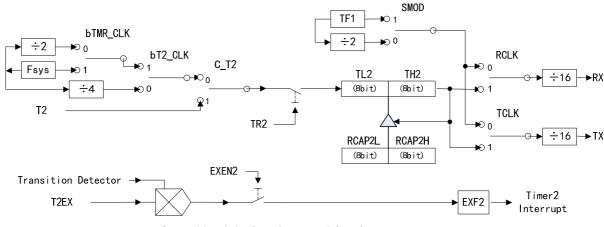

- UART: 4 UARTs. UART0 is a standard MCS51 UART. UART1, UART2 and UART3 have built-in communication baud rate setting register.

- SPI: The SPI controller supports Master/Slave mode, with built-in FIFO, clock frequency can be approximate to Fsys/2. It supports simplex multiplexing of serial data input and output.

- ADC: 12-channel 12-bit A/D converter, it supports voltage comparison of multiple combinations.

- Touch-key: 12-channel capacitive touch-key detection. Each ADC channel supports touch-key detection.

- TS: Built-in simple temperature sensor.

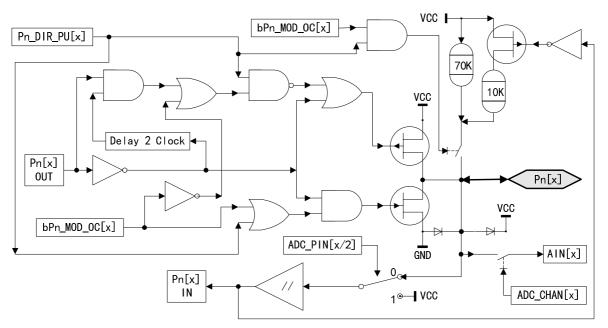

- GPIO: Supports up to 44 GPIO pins (including XI, RST and USB signal pins), support MCS51 compatible quasi-bidirectional mode, newly add high-impedance input, push-pull output, open-drain output modes, one of these pins supports 12V high-voltage open-drain output.

- Interrupt: Supports 16 interrupt sources, including 6 interrupts compatible with the standard MCS51 (INT0, T0, INT1, T1, UART0, T2), and 10 extended interrupts (SPI0, INT3, USB, ADC/UART2, UART1, PWMX/UART3, GPIO, WDOG). GPIO interrupt can be selected from 7 pins.

- Watch-Dog: 8-bit presettable watchdog timer WDOG, support timer interrupt.

- Reset: Supports 5 reset sources, built-in power on reset and multi-stage adjustable power supply low voltage detection reset module, supports software reset and watchdog overflow reset, configurable external input reset.

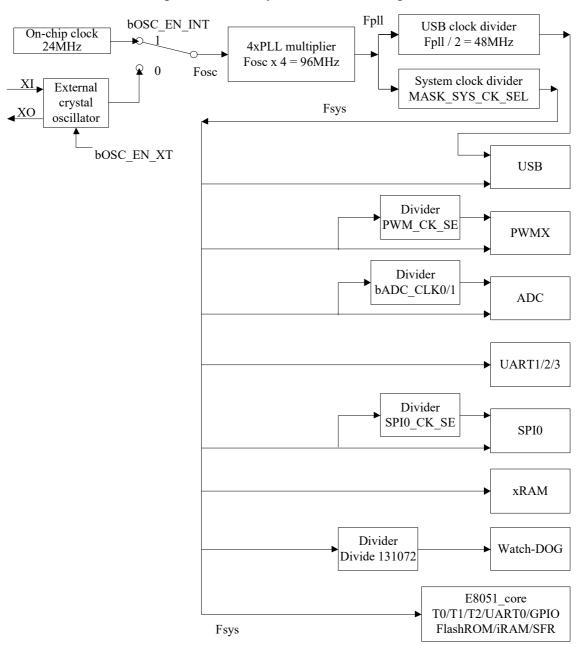

- Clock: Built-in 24MHz clock, support external crystal oscillator through alternate GPIO pins, built-in PLL for USB clock and Fsys.

- Power: Built-in 5V to 3.3V LDO for USB and other modules; it supports 5V, 3.3V, even 6V and 2.8V voltage input.

- Sleep: Supports low power Sleep mode, supports USB, UART0, UART1, SPI0, comparator and some GPIOs wake-up.

- Unique ID for identification.

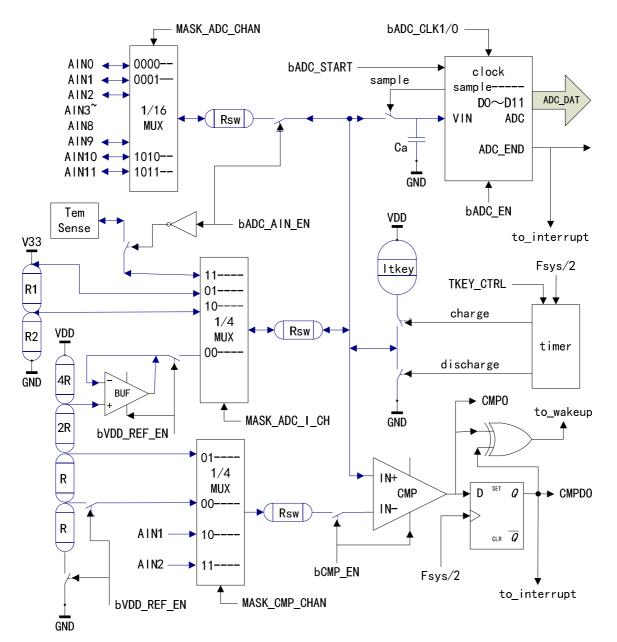

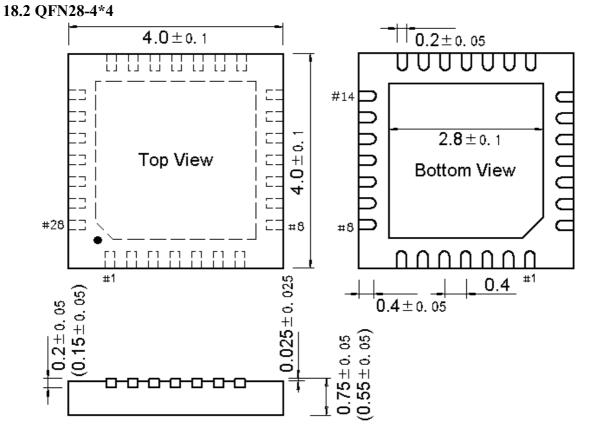

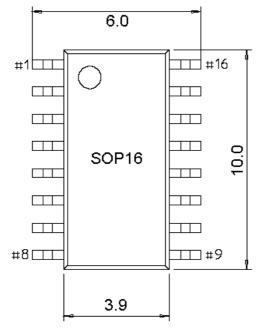

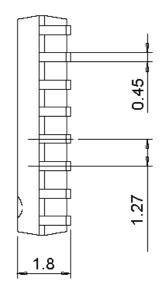

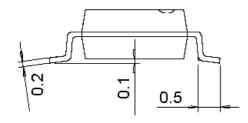

# 3. Package

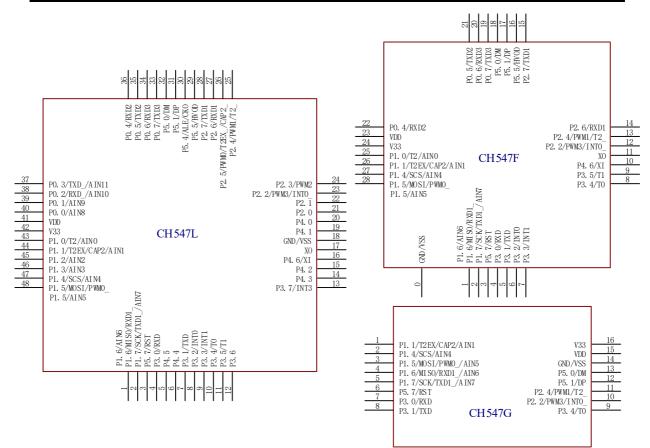

| Package   | Body size |        | Lead pitch |         | Description                   | Part No. |

|-----------|-----------|--------|------------|---------|-------------------------------|----------|

| LQFP-48   | 7*7mm     |        | 0.5mm      | 19.7mil | Standard LQFP<br>48-pin patch | CH547L   |

| QFN28_4X4 | 4*4mm     |        | 0.4mm      | 15.7mil | Quad no-lead 28-pin           | CH547F   |

| SOP-16    | 3.9mm     | 150mil | 1.27mm     | 50mil   | Standard 16-pin<br>patch      | CH547G   |

| LQFP-48   | 7*7mm     |        | 0.5mm      | 19.7mil | Standard LQFP<br>48-pin patch | CH546L   |

| SOP-16    | 3.9mm     | 150mil | 1.27mm     | 50mil   | Standard 16-pin<br>patch      | CH546G   |

# 4. Pin definitions

| SOP16 | Pin No.<br>QFN28 | LQFP48 | Pin<br>Name | Alternate<br>(Left preferential) | Description                                                                                                                                                     |

|-------|------------------|--------|-------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | 23               | 41     | VDD         | VCC                              | I/O power input and external power input of internal USB power regulator, requires an external 0.1uF decoupling capacitor.                                      |

| 16    | 24               | 42     | V33         | V3                               | Internal voltage regulator output and internal USB<br>power input,<br>When supply voltage is less than 3.6V, connect<br>VDD to input the external power supply. |

| -         -         38         PO.2         RXD_/AIN10         signal/touch-key input.           -         -         37         PO.3         TXD_/AIN11         RXD_, TXD_, T  |      |      |    |       |                 | When supply voltage is greater than 3.6V, an          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----|-------|-----------------|-------------------------------------------------------|

| -         -         40         P0.0         AIN8         AIN8         AIN8         AIN8         -         AIN11         4-channel         ADC         analo           -         -         38         P0.2         RXD_/AIN10         RXD_, TXD_, TXD_, TXD_, TXD_ pin mapping.           -         -         37         P0.3         TXD_/AIN10         RXD_, TXD_, TXD_, TXD_, TXD_, TXD_, TXD_, SCD_, S                                                                                                                                        |      |      |    |       |                 | external 0.1uF decoupling capacitor is required.      |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14   | 0    | 18 | GND   | VSS             | Ground                                                |

| -       -       38       P0.2       RXD_/AIN10       signal/touch-key input.         -       -       37       P0.3       TXD_/AIN11       RXD_, TXD_: RXD, TXD pin mapping.         -       22       36       P0.4       RXD2       wutput.         -       21       35       P0.5       TXD_       RXD2, TXD2: UART3 serial data input, serial dat output.         -       20       34       P0.6       RXD3       wutput.         -       20       34       P1.0       T2/AIN0       AIN0 ~ AIN7: 8-channel ADC analo signal/touch-key input.         -       25       43       P1.2       AIN2       T2: Timer/counter2 external count input/clock output rutput.         -       -       45       P1.2       AIN3       CAP2: Timer/counter2 reload/capture input.         2       27       47       P1.4       SCS/AIN4       SCS.       SCS. MOSI, MISO, SCK: SPI0 interfaces. SCS         4       1       1       P1.6       MISO/RXD1_/AIN6       MISO is master output/slave output, SCK is serie clock.         5       2       2       P1.7       SCK/TXD1_/AIN7       PWM0_PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM0/TZE_/CAP2 T2EX/CAP2_i T2EX/CAP2 pin mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -    | -    | 40 | P0.0  | AIN8            |                                                       |

| -         -         38         P0.2         PXD_/AIN10         RXD_/TXD_: RXD_, TXD pin mapping.           -         21         35         P0.4         RXD_2         RXD_2, TXD2: UART2 serial data input, serial data output.           -         21         35         P0.6         RXD3         RXD3, TXD3: UART3 serial data input, serial data output.           -         20         34         P0.6         RXD3         output.           -         20         34         P0.6         RXD3         output.           -         20         34         P0.6         RXD3         output.           -         25         43         P1.0         T2/AIN0         AIN0         AIN7: 8-channel ADC analo output.           -         46         P1.3         AIN3         T2EX: Timer/counter2 catternal count input/clock output           -         -         46         P1.3         AIN3         CAP2: Timer/counter2 catternal count input/clock output           2         27         47         P1.4         SCS/AIN4         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS           4         1         1         P1.6         MISO/RXD1/AIN7         MISO is master output/slave input           -         21         P2.0         PXM0/PWM3: 4-ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    | -    | 39 | P0.1  | AIN9            | 5                                                     |

| -       -       37       P0.3       FXD_/AIN11       RXD_/AIN11         -       22       36       P0.4       RXD2         -       21       35       P0.6       RXD3         -       20       34       P0.6       RXD3         -       19       33       P0.7       TXD3         -       25       43       P1.0       T2/AIN0       AIN0 ~ AIN7:       8-channel ADC analo utput.         -       25       43       P1.0       T2/AIN0       AIN0 ~ AIN7:       8-channel ADC analo utput.         -       25       43       P1.0       T2/AIN0       AIN0 ~ AIN7:       8-channel ADC analo utput.         -       46       P1.3       AIN3       T2EX: Timer/counter2 eload/capture input.         2       27       47       P1.4       SCS/AIN4       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         4       1       1       P1.6       MISO/RXD1_/AIN6       HISO is master input/slave output, SCK is serie clock.         5       2       2       P1.7       SCK/TXD1_/AIN7       PWM0_PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM0/TIZE       T2.:T2 pin mapping.         -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | -    | 38 | P0.2  | RXD_/AIN10      |                                                       |

| -         22         36         P0.4         RXD2         output.           -         21         35         P0.5         TXD2         RXD3, TXD3: UART3 serial data input, serial data output.           -         20         34         P0.6         RXD3         output.           -         19         33         P0.7         TXD3         analo           -         25         43         P1.0         T2/AIN0         AIN0 ~ AIN7: 8-channel ADC analo           1         26         44         P1.1         T2EX/CAP2/AIN1         signal/touch-key input.           -         45         P1.2         AIN2         T2: Timer/counter2 external count input/clock output           -         46         P1.3         AIN3         T2EX: Timer/counter2 capture input.           2         27         47         P1.4         SCS/AIN4         CAP2: Timer/counter2 capture input.           3         28         48         P1.5         MOS/PWM0_/AIN5         SCS, MOSI, MISO, SCK: SP10 interfaces. SCS           4         1         1         P1.6         MISO/RXD1_/AIN7         MK50 is master input/slave output, SCK is serial clock.           7         2         P2.1         P2.0         PXM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -    | -    | 37 | P0.3  | TXD_/AIN11      |                                                       |

| -       21       35       P0.5       TXD2       RXD3, TXD3: UART3 serial data input, serial data output.         -       19       33       P0.7       TXD3       output.         -       19       33       P0.7       TXD3       output.         -       25       43       P1.0       T2/AIN0       AIN0 ~ AIN7: 8-channel ADC analo signal/touch-key input.         -       -       45       P1.2       AIN2       T2: Timer/counter2 external count input/clock output         -       -       46       P1.3       AIN3       T2EX: Timer/counter2 capture input.         2       27       47       P1.4       SCS/AIN4       CAP2: Timer/counter2 capture input.         3       28       48       P1.5       MOSI/PWM0_/AIN5       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         4       1       1       P1.6       MISO/RXD1_/AIN6       MISO is master input/slave output/slave input         5       2       2       P1.7       SCK/TXD1_/AIN6       MISO is master input/slave output/slave input         10       12       23       P2.0       PWM0_RXD1_TXD1_       INT0_: INT0 in mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -    | 22   | 36 | P0.4  | RXD2            |                                                       |

| -       20       34       P0.6 [RXD3       output.         -       19       33       P0.7 [TXD3       output.         -       25       43       P1.0 [72/AIN0       AIN0 ~ AIN7: 8-channel ADC analo signal/touch-key input.         -       26       44       P1.1 [T2EX/CAP2/AIN1]       signal/touch-key input.         -       -       45       P1.2       AIN2       T2: Timer/counter2 external count input/clock output         2       27       47       P1.4       SCS/AIN4       CAP2: Timer/counter2 external count input/clock output         3       28       48       P1.5       MOSI/PWM0_/AIN5       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         4       1       1       P1.6       MISO/RXD1_/AIN6       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         5       2       2       P1.7       SCK/TXD1_/AIN7       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         6       8       P2.2       P2.0       PWM0_RXD1_TXD1_: PWM0/RXD1/TXD1 pi mapping.         -       -       21       P2.0       PWM0_RXD2_T2X_/CAP2         -       -       22       P2.1       INT0_: INT0 in mapping.         11       13       25       P2.4       PWM1/T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 21   | 35 | P0.5  | TXD2            | 1                                                     |

| -         19         33         P0.7         TXD3           -         25         43         P1.0         T2/AIN0         AIN0         ~ AIN7:         8-channel         ADC         analo           1         26         44         P1.1         T2EX/CAP2/AIN1         signal/touch-key input.           -         -         45         P1.2         AIN3         T2EX: Timer/counter2 external count input/clock output           -         -         46         P1.3         AIN3         T2EX: Timer/counter2 reload/capture input.           2         27         47         P1.4         SCS/AIN4         CAP2: Timer/counter2 capture input.           3         28         48         P1.5         MOSI/PWM0_/AIN5         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS           4         1         1         P1.6         MISO/RXD1_/AIN6         MISO is master input/slave output, SCK is seria clock.           5         2         2         P1.7         SCK/TXD1_/AIN7         PWM0_RXD1_TXD1_: TXD1_: PWM0/RXD1/TXD1 pi mapping.           -         -         21         P2.0         P2.0         PWM0_RXD1_TXD2_: T2 pi mapping.           -         -         22         P2.1         PWM0/MO_RXD1_TZ_: T2 pi mapping.         T2 : T2 pi mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -    | 20   | 34 | P0.6  | RXD3            | _                                                     |

| 1       26       44       P1.1       T2EX/CAP2/AIN1       signal/touch-key input.         -       -       45       P1.2       AIN2       T2: Timer/counter2 external count input/clock output         2       27       47       P1.4       SCS/AIN4       CAP2: Timer/counter2 capture input.         3       28       48       P1.5       MOSL/PWM0_/AIN5       SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS         4       1       1       P1.6       MISO/RXD1_/AIN6       MISO is master input/slave output, SCK is serial clock.         5       2       2       P1.7       SCK/TXD1_/AIN7       PWM0_RXD1_, TXD1_: PWM0/RXD1/TXD1 pi mapping.         -       -       21       P2.0       P2.1       PWM0-PWM3; 4-channel PWM outputs.         10       12       23       P2.2       PWM1/T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -    | 19   | 33 | P0.7  | TXD3            | oupu.                                                 |

| -         45         P1.2         AIN2         T2: Timer/counter2 external count input/clock output           -         46         P1.3         AIN3         T2EX: Timer/counter2 external count input/clock output           2         27         47         P1.4         SCS/AIN4         CAP2: Timer/counter2 external count input/clock output           3         28         48         P1.5         MOSI/PWM0_/AIN5         CAP2: Timer/counter2 capture input.           4         1         1         P1.6         MISO/RXD1_/AIN6         CAP2: Timer/counter2 external count input/clock output           5         2         2         P1.7         SCK/TXD1_/AIN7         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS           6         P2.0         -         -         21         P2.0         -           -         21         P2.0         -         -         22         P2.1         PWM0-PWM3: 4-channel PWM outputs.           10         12         23         P2.2         PWM3/INT0_         INT0_: INT0 pin mapping.           -         -         24         P2.3         PWM2         T2: X_CAP2_: T2EX/CAP2 pin mapping.           -11         13         25         P2.4         PWM0/T2EX_/CAP2.         T2EX_/CAP2.: T2EX/CAP2 pin mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 25   | 43 | P1.0  | T2/AIN0         | AIN0 ~ AIN7: 8-channel ADC analog                     |

| -         46         P1.3         AIN3         T2EX: Timer/counter2 reload/capture input.           2         27         47         P1.4         SCS/AIN4         CAP2: Timer/counter2 capture input.           3         28         48         P1.5         MOSI/PWM0_/AIN5         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS           4         1         1         P1.6         MISO/RXD1_/AIN6         chip select input, MOSI is master output/slave input           5         2         2         P1.7         SCK/TXD1_/AIN7         MISO is master input/slave output, SCK is serie clock.           5         2         2         P1.7         SCK/TXD1_/AIN7         PWM0-PWM3: 4-channel PWM outputs.           10         12         23         P2.2         PWM1/T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1    | 26   | 44 | P1.1  | T2EX/CAP2/AIN1  | signal/touch-key input.                               |

| 2         27         47         P1.4         SCS/AIN4         CAP2: Timer/counter2 capture input.           3         28         48         P1.5         MOSI/PWM0_/AIN5         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS chip select input, MOSI is master output/slave input           4         1         1         P1.6         MISO/RXD1_/AIN6         SCS, MOSI, MISO, SCK: SPI0 interfaces. SCS chip select input, MOSI is master output/slave input           5         2         2         P1.7         SCK/TXD1_/AIN7         MISO is master input/slave output, SCK is serial clock.           7         -         21         P2.0         PWM0_RXD1_, TXD1_: PWM0/RXD1/TXD1 pi mapping.           -         -         22         P2.1         PWM0/PWM3: 4-channel PWM outputs.           10         12         23         P2.2         PWM3/INT0_         T1.7           11         13         25         P2.4         PWM1/T2_         T2_: T2 pin mapping.           -         -         26         P2.5         PWM0/T2EX_/CAP2         RXD1, TXD1: UART1 serial data input, serial dat           -         14         27         P2.6         RXD         RXD, TXD: UART0 serial data input, serial dat           -         15         28         P2.7         TXD1         T0, T1: Timer0, timer1 external interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -    | -    | 45 | P1.2  | AIN2            | T2: Timer/counter2 external count input/clock output. |

| 2       27       17       111       DSDAMT         3       28       48       P1.5       MOSI/PWM0_/AIN5       SCS, MOSI, MISO, SCE: SP10 interfaces. SCS chip select input, MOSI is master output/slave input/Slave inpu | -    | -    | 46 | P1.3  | AIN3            | 1 1                                                   |

| 5       20       100       11.0       MISO/IT WING/ITH 10         4       1       1       P1.6       MISO/RXD1/AIN6       chip select input, MOSI is master output/slave input/<br>MISO is master input/slave output, SCK is serie clock.<br>PWM0_RXD1_, TXD1_: PWM0/RXD1/TXD1 pi mapping.         5       2       2       P1.7       SCK/TXD1_/AIN7       clock.<br>PWM0_RXD1_, TXD1_: PWM0/RXD1/TXD1 pi mapping.         -       -       21       P2.0       PWM0_PWM3: 4-channel PWM outputs.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2       RXD1, TXD1: UART1 serial data input, serial data input, serial data         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD         -       15       28       P2.7       TXD1         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         - <t< td=""><td>2</td><td>27</td><td>47</td><td>P1.4</td><td>SCS/AIN4</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2    | 27   | 47 | P1.4  | SCS/AIN4        |                                                       |

| 4       1       1       11.0       MISO KKD1_AINO         5       2       2       P1.7       SCK/TXD1_/AIN7       MISO is master input/slave output, SCK is serial clock.         5       2       2       P1.7       SCK/TXD1_/AIN7       MISO is master input/slave output, SCK is serial clock.         6       -       22       P2.1       PWM0-PWM3: 4-channel PWM outputs.       INT0_: INT0 pin mapping.         10       12       23       P2.2       PWM3/INT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3    | 28   | 48 | P1.5  | MOSI/PWM0_/AIN5 |                                                       |

| 5       2       2       P1.7       SCK/TXD1_/AIN7       clock.<br>PWM0_, RXD1_, TXD1_: PWM0/RXD1/TXD1 pi<br>mapping.         -       -       21       P2.0       PWM0-PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM1/T0_       INT0_: INT0 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2       RXD1, TXD1 vertal data input, serial data output.         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD         -       12       P3.6       INT0       output.         -       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       INT3         -       -       12       P3.6       INT3         -       -       13       P3.7       INT3         -       -       19       P4.1       INT3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4    | 1    | 1  | P1.6  | MISO/RXD1_/AIN6 |                                                       |

| 5       2       2       P1.7       SCK/TXD1_/AIN7       PWM0_, RXD1_, TXD1_: PWM0/RXD1/TXD1 pi mapping.         -       -       21       P2.0       PWM0_PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM1/T0_       PWM0-PWM3: 4-channel PWM outputs.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         -       -       24       P2.3       PWM1/T2       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/TXCAP2       RXD1         -       14       27       P2.6       RXD1       autoptic.         -       15       28       P2.7       TXD1       RXD, TXD: UART1 serial data input, serial data output.         -       15       28       P2.7       TXD1       RXD, TXD: UART0 serial data input, serial data output.         -       15       28       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         -       7       9       P3.4       T0       input.       T0, T1: Timer0, timer1 external input.         -       12<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |    |       |                 |                                                       |

| -       -       21       P2.0         -       -       22       P2.1         10       12       23       P2.2       PWM3/INT0_         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         11       13       25       P2.4       PWM1/T2_       T2EX_/CAP2_: T2EX/CAP2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2_       RXD1, TXD1: UART1 serial data input, serial data         -       14       27       P2.6       RXD       RXD         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD         -       7       9       P3.3       INT1         9       8       10       P3.4       T0         -       9       11       P3.5       T1         -       -       12       P3.6       INT3         -       -       12       P3.6       INT3         -       -       19       P4.1       Y1         -       -       19       P4.1       Y1         -       -       14       P4.3       P4.3 </td <td>5</td> <td>2</td> <td>2</td> <td>P1.7</td> <td>SCK/TXD1 /AIN7</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5    | 2    | 2  | P1.7  | SCK/TXD1 /AIN7  |                                                       |

| -       21       P2.0         -       22       P2.1       PWM0-PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM3/INT0_       INT0_: INT0 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         11       13       25       P2.4       PWM1/T2_       T2_: T2 EX/CAP2_ in mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2_       RXD1, TXD1: UART1 serial data input, serial data output.         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1       RXD, TXD: UART0 serial data input, serial data output.         -       15       28       P2.7       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       INT3: External interrupt3.         -       -       13       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |    |       | _               |                                                       |

| -       -       22       P2.1       PWM0~PWM3: 4-channel PWM outputs.         10       12       23       P2.2       PWM3/INT0_       INT0_: INT0 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         11       13       25       P2.4       PWM1/T2_       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2_       RXD1, TXD1: UART1 serial data input, serial data         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt         9       8       10       P3.4       T0       input.       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3       INT3: External interrupt3.         -       -       19       P4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      | 21 | D2 () |                 | mapping.                                              |

| 10       12       23       P2.2       PWM3/INT0_       INT0_: INT0 pin mapping.         -       -       24       P2.3       PWM2       T2_: T2 pin mapping.         11       13       25       P2.4       PWM1/T2_       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2       RXD1, TXD1: UART1 serial data input, serial data input, serial data output.         -       14       27       P2.6       RXD1       RXD1         -       15       28       P2.7       TXD1       RXD, TXD: UART1 serial data input, serial data output.         -       15       28       P2.7       TXD1       RXD, TXD: UART0 serial data input, serial data output.         -       15       28       P3.2       INT0       output.         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3       INT3: External interrupt3.         -       -       19       P4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | -    |    |       |                 | DWA (0, DWA (2, 4, shows st DWA (, sectors))          |

| -       24       P2.3       PWM2       T2_: T2 pin mapping.         11       13       25       P2.4       PWM1/T2_       T2_: T2 pin mapping.         -       -       26       P2.5       PWM0/T2EX_/CAP2_       RXD1, TXD1: UART1 serial data input, serial data         -       14       27       P2.6       RXD1       RXD1, TXD1: UART1 serial data input, serial data         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD         -       6       8       P3.2       INT0         -       7       9       P3.3       INT1         INT0, INT1: External interrupt0, external interrupt0       external interrupt1         9       8       10       P3.4       T0         -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       Y1         -       -       14       P4.3       Y1         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - 10 | - 12 |    |       | PWM3/INT0       |                                                       |

| 11       13       25       P2.4       PWM1/T2_       T2EX/CAP2 : T2EX/CAP2 pin mapping.         -       26       P2.5       PWM0/T2EX_/CAP2       RXD1       T2EX/CAP2 : T2EX/CAP2 pin mapping.         -       14       27       P2.6       RXD1       RXD1: UART1 serial data input, serial data input, serial data output.         -       15       28       P2.7       TXD1       TXD         7       4       4       P3.0       RXD       RXD, TXD: UART0 serial data input, serial data output.         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.       T3: External interrupt3.         -       -       19       P4.1       INT3:       INT3: External crystal oscillator input, inverte         -       -       14       P4.3       INT4:       INT4: Context       Context <td></td> <td></td> <td></td> <td></td> <td>— —</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |    |       | — —             |                                                       |

| -       -       26       P2.5       PWM0/T2EX_/CAP2_       RXD1, TXD1: UART1 serial data input, serial data         -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1       output.         7       4       4       P3.0       RXD       RXD, TXD: UART0 serial data input, serial data         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       XI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |    |       |                 |                                                       |

| -       14       27       P2.6       RXD1       output.         -       15       28       P2.7       TXD1       output.         7       4       4       P3.0       RXD       RXD         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       6       8       P3.2       INT0       INT0, INT1: External interrupt0, external interrupt0, external interrupt0, external input.         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       XI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | -    |    |       |                 |                                                       |

| -       15       28       P2.7       TXD1         7       4       4       P3.0       RXD         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       XI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    | 14   |    |       |                 |                                                       |

| 7       4       4       P3.0       RXD         8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data output.         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       XI, XO: External crystal oscillator input, inverter         -       -       14       P4.3       output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -    |      |    |       |                 |                                                       |

| 8       5       7       P3.1       TXD       RXD, TXD: UART0 serial data input, serial data         -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       XI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7    |      |    |       |                 |                                                       |

| -       6       8       P3.2       INT0       output.         -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt0         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       9       11       P3.5       T1       INT3: External interrupt3.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       19       P4.1       YI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |    |       |                 | RXD_TXD: UART0_serial_data_input_serial_data          |

| -       7       9       P3.3       INT1       INT0, INT1: External interrupt0, external interrupt         9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3       INT3: External interrupt3.         -       -       13       P3.7       INT3       INT3: External crystal oscillator input, inverte         -       -       15       P4.2       XI, XO: External crystal oscillator input, inverte         -       -       14       P4.3       Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |    |       |                 |                                                       |

| 9       8       10       P3.4       T0       input.         -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       T0, T1: Timer0, timer1 external input.         -       -       13       P3.7       INT3         -       -       20       P4.0       P4.1         -       -       15       P4.2       XI, XO: External crystal oscillator input, inverte output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -    |      |    |       |                 |                                                       |

| -       9       11       P3.5       T1       T0, T1: Timer0, timer1 external input.         -       -       12       P3.6       INT3: External interrupt3.         -       -       13       P3.7       INT3         -       -       20       P4.0       INT3: External interrupt3.         -       -       19       P4.1       INT3: External crystal oscillator input, inverte output.         -       -       14       P4.3       Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9    | 8    | 10 |       |                 |                                                       |

| -         12         P3.6         INT3: External interrupt3.           -         -         13         P3.7         INT3           -         -         20         P4.0         P4.1           -         -         15         P4.2         XI, XO: External crystal oscillator input, inverte output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -    | 9    | 11 | P3.5  | T1              | -                                                     |

| -         -         13         P3.7         INT3           -         -         20         P4.0         P4.1           -         -         15         P4.2         XI, XO: External crystal oscillator input, inverte output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | -    | 12 |       |                 | INT3: External interrupt3.                            |

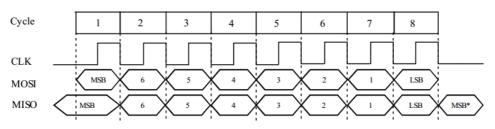

| -         19         P4.1           -         -         15         P4.2           -         -         14         P4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -    | -    |    |       | INT3            |                                                       |